商机详情 -

湖州镍刻蚀

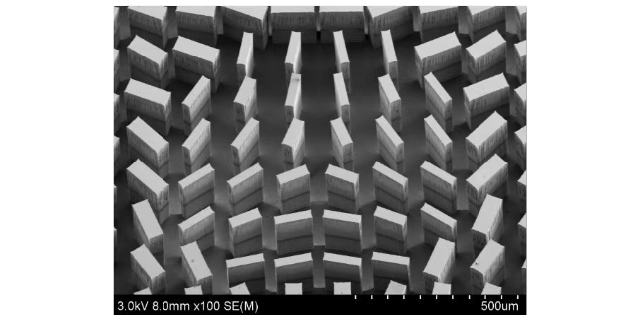

刻蚀技术是一种在集成电路制造中广泛应用的重要工艺。它是一种通过化学反应和物理过程来去除或改变材料表面的方法,可以用于制造微小的结构和器件。以下是刻蚀技术在集成电路制造中的一些应用:1.制造光刻掩膜:刻蚀技术可以用于制造光刻掩膜。光刻掩膜是一种用于制造微小结构的模板,它可以通过刻蚀技术来制造。在制造过程中,先在掩膜上涂上光刻胶,然后使用光刻机器将图案投射到光刻胶上,之后使用刻蚀技术将光刻胶和掩膜上不需要的部分去除。2.制造微机电系统(MEMS):刻蚀技术可以用于制造微机电系统(MEMS)。MEMS是一种微小的机械系统,可以用于制造传感器、执行器和微型机器人等。通过刻蚀技术,可以在硅片表面形成微小的结构和器件,从而制造MEMS。刻蚀技术可以通过选择不同的刻蚀气体和压力来实现不同的刻蚀效果。湖州镍刻蚀

刻蚀技术,是在半导体工艺,按照掩模图形或设计要求对半导体衬底表面或表面覆盖薄膜进行选择性腐蚀或剥离的技术。刻蚀技术不仅是半导体器件和集成电路的基本制造工艺,而且还应用于薄膜电路、印刷电路和其他微细图形的加工。刻蚀还可分为湿法刻蚀和干法刻蚀。普通的刻蚀过程大致如下:先在表面涂敷一层光致抗蚀剂,然后透过掩模对抗蚀剂层进行选择性曝光,由于抗蚀剂层的已曝光部分和未曝光部分在显影液中溶解速度不同,经过显影后在衬底表面留下了抗蚀剂图形,以此为掩模就可对衬底表面进行选择性腐蚀。如果衬底表面存在介质或金属层,则选择腐蚀以后,图形就转移到介质或金属层上。珠海氮化硅材料刻蚀外协刻蚀技术可以实现对材料的选择性刻蚀,从而制造出复杂的微纳结构。

反应离子刻蚀:这种刻蚀过程同时兼有物理和化学两种作用。辉光放电在零点几到几十帕的低真空下进行。硅片处于阴极电位,放电时的电位大部分降落在阴极附近。大量带电粒子受垂直于硅片表面的电场加速,垂直入射到硅片表面上,以较大的动量进行物理刻蚀,同时它们还与薄膜表面发生强烈的化学反应,产生化学刻蚀作用。选择合适的气体组分,不仅可以获得理想的刻蚀选择性和速度,还可以使活性基团的寿命短,这就有效地阻止了因这些基团在薄膜表面附近的扩散所能造成的侧向反应,较大提高了刻蚀的各向异性特性。反应离子刻蚀是超大规模集成电路工艺中比较有发展前景的一种刻蚀方法

刻蚀工艺去除晶圆表面的特定区域,是以沉积其它材料。“干法”(等离子)刻蚀用于形成电路,而“湿法”刻蚀(使用化学浴)主要用于清洁晶圆。干法刻蚀是半导体制造中较常用的工艺之一。开始刻蚀前,晶圆上会涂上一层光刻胶或硬掩膜(通常是氧化物或氮化物),然后在光刻时将电路图形曝光在晶圆上。刻蚀只去除曝光图形上的材料。在芯片工艺中,图形化和刻蚀过程会重复进行多次,贵州深硅刻蚀材料刻蚀价钱,贵州深硅刻蚀材料刻蚀价钱。等离子刻蚀是将电磁能量(通常为射频(RF))施加到含有化学反应成分(如氟或氯)的气体中实现。等离子会释放带正电的离子来撞击晶圆以去除(刻蚀)材料,并和活性自由基产生化学反应,与刻蚀的材料反应形成挥发性或非挥发性的残留物。离子电荷会以垂直方向射入晶圆表面。这样会形成近乎垂直的刻蚀形貌,这种形貌是现今密集封装芯片设计中制作细微特征所必需的。刻蚀技术可以实现不同形状的刻蚀,如线形、点形、面形等。

选择比指的是在同一刻蚀条件下一种材料与另一种材料相比刻蚀速率快多少,它定义为被刻蚀材料的刻蚀速率与另一种材料的刻蚀速率的比。基本内容:高选择比意味着只刻除想要刻去的那一层材料。一个高选择比的刻蚀工艺不刻蚀下面一层材料(刻蚀到恰当的深度时停止)并且保护的光刻胶也未被刻蚀。图形几何尺寸的缩小要求减薄光刻胶厚度。高选择比在较先进的工艺中为了确保关键尺寸和剖面控制是必需的。特别是关键尺寸越小,选择比要求越高。广东省科学院半导体研究所。材料刻蚀是一种重要的微纳加工技术,可用于制造微电子器件和MEMS器件。合肥半导体刻蚀

材料刻蚀是一种重要的微纳加工技术,可用于制造微电子器件和光学元件。湖州镍刻蚀

反应离子刻蚀是当前常用技术路径,属于物理和化学混合刻蚀。在传统的反应离子刻蚀机中,进入反应室的气体会被分解电离为等离子体,等离子体由反应正离子、自由基,浙江氮化硅材料刻蚀服务价格、反应原子等组成。反应正离子会轰击硅片表面形成物理刻蚀,同时被轰击的硅片表面化学活性被提高,之后硅片会与自由基和反应原子形成化学刻蚀。这个过程中由于离子轰击带有方向性,RIE技术具有较好的各向异性。目前先进集成电路制造技术中用于刻蚀关键层的刻蚀方法是高密度等离子体刻蚀技术。传统的RIE系统难以使刻蚀物质进入高深宽比图形中并将残余生成物从中排出,因此不能满足0.25μm以下尺寸的加工要求,解决办法是增加等离子体的密度。高密度等离子体刻蚀技术主要分为电子回旋加速振荡(ECR)、电容或电感耦合等离子体(CCP/ICP)。刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称。湖州镍刻蚀