商机详情 -

安徽40VSGTMOSFET行业

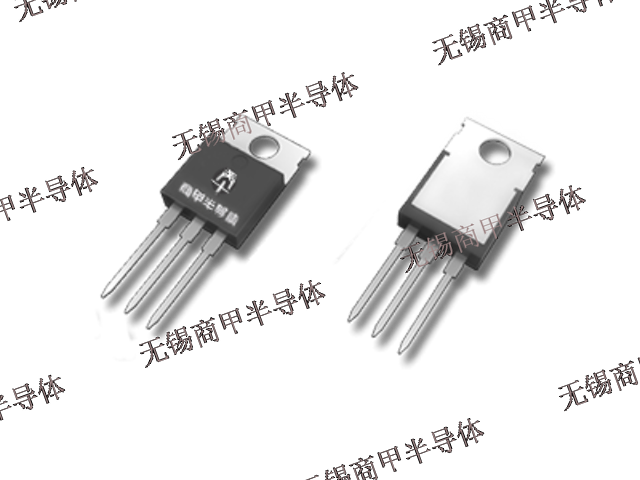

SGTMOSFET制造:芯片封装芯片封装是SGTMOSFET制造的一道重要工序。封装前,先对晶圆进行切割,将其分割成单个芯片,切割精度要求达到±20μm。随后,选用合适的封装材料与封装形式,常见的有TO-220、TO-247等封装形式。以TO-220封装为例,将芯片固定在引线框架上,采用银胶粘接,确保芯片与引线框架电气连接良好,银胶固化温度在150-200℃,时间为30-60分钟。接着,通过金丝键合实现芯片电极与引线框架引脚的连接,键合拉力需达到5-10g。用环氧树脂等封装材料进行灌封,固化温度在180-220℃,时间为1-2小时,保护芯片免受外界环境影响,提高器件的机械强度与电气性能稳定性,使制造完成的SGTMOSFET能够在各类应用场景中可靠运行。3D 打印机的电机驱动电路采用 SGT MOSFET对打印头移动与成型平台升降的精确控制提高 3D 打印的精度与质量。安徽40VSGTMOSFET行业

SGTMOSFET的栅极电荷特性对其性能影响深远。低栅极电荷(Qg)意味着在开关过程中所需的驱动能量更少。在高频开关应用中,这一特性可大幅降低驱动电路的功耗,提高系统整体效率。以无线充电设备为例,SGTMOSFET低Qg的特点能使设备在高频充电过程中保持高效,减少能量损耗,提升充电速度与效率。在实际应用中,低栅极电荷使驱动电路设计更简单,减少元件数量,降低成本,同时提高设备可靠性。如在智能手表的无线充电模块中,SGTMOSFET凭借低Qg优势,可在小尺寸空间内实现高效充电,延长手表电池续航时间,提升用户体验,推动无线充电技术在可穿戴设备领域的广泛应用。SOT-23SGTMOSFET智能系统SGT MOSFET 以低导通电阻,降低电路功耗,适用于手机快充,提升充电速度。

多沟槽协同设计与元胞优化为实现更高功率密度,SGTMOSFET采用多沟槽协同设计:1场板沟槽,通过引入与漏极相连的场板,平衡体内电场分布,抑制动态导通电阻(RDS(on))的电流崩塌效应;2源极接触沟槽,缩短源极金属与硅片的接触距离,降低接触电阻(Rcontact)3栅极分割沟槽,将栅极分割为多个单一单元,减少栅极电阻(Rg)和栅极延迟时间(td)。通过0.13μm超细元胞工艺,元胞密度提升50%,RDS(on)进一步降低至33mΩ·mm²(100V产品)。

SGTMOSFET的结构创新在于引入了屏蔽栅。这一结构位于沟槽内部,多晶硅材质的屏蔽栅极处于主栅极上方。在传统沟槽MOSFET中,电场分布相对单一,而SGTMOSFET的屏蔽栅能够巧妙地调节沟道内电场。当器件工作时,电场不再是简单的三角形分布,而是在屏蔽栅的作用下,朝着更均匀、更高效的方向转变。这种电场分布的优化,降低了导通电阻,提升了开关速度。例如,在高频开关电源应用中,SGTMOSFET能以更快速度切换导通与截止状态,减少能量在开关过程中的损耗,提高电源转换效率,为电子产品的高效运行提供有力支持。SGT MOSFET 结构中的 CD - shield 和 Rshield 寄生元件能够吸收器件关断时 dv/dt 变化产生的尖峰和震荡降低电磁干扰.

SGTMOSFET在工作过程中会产生一定的噪声,包括开关噪声和电磁辐射噪声。为抑制噪声,可以采取多种方法。在电路设计方面,优化PCB布局,减少寄生电感和电容,例如将功率回路和控制回路分开,缩短电流路径。在器件选型上,选择低噪声的SGTMOSFET,其栅极电荷和开关损耗较低,能够减少噪声产生。此外,还可以在电路中添加滤波电路,如LC滤波器,对噪声进行滤波处理。通过这些方法的综合应用,可以有效降低SGTMOSFET的噪声,满足电子设备对电磁兼容性的要求。屏蔽栅降米勒电容,SGT MOSFET 减少电压尖峰,稳定电路运行。安徽100VSGTMOSFET规范大全

SGT MOSFET 成本效益高,高性能且价格实惠。安徽40VSGTMOSFET行业

设计挑战与解决方案SGTMOSFET的设计需权衡导通电阻与耐压能力。高单元密度可能引发栅极寄生电容上升,导致开关延迟。解决方案包括优化屏蔽电极布局(如分裂栅设计)和使用先进封装(如铜夹键合)。此外,雪崩击穿和热载流子效应(HCI)是可靠性隐患,可通过终端结构(如场板或结终端扩展)缓解。仿真工具(如SentaurusTCAD)在器件参数优化中发挥关键作用,帮助平衡性能与成本,设计方面往新技术去研究,降低成本,提高性能,做的高耐压低内阻安徽40VSGTMOSFET行业