商机详情 -

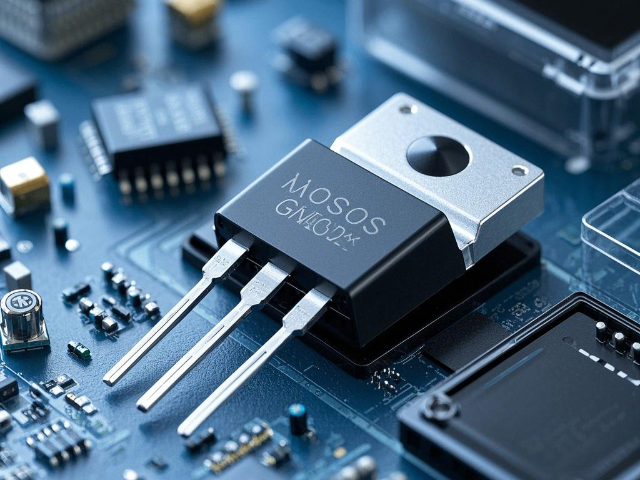

有什么MOS代理商

MOSFET是数字集成电路的基石,尤其在CMOS(互补金属氧化物半导体)技术中,NMOS与PMOS的互补结构彻底改变了数字电路的功耗与集成度。CMOS反相器是较基础的单元:当输入高电平时,PMOS截止、NMOS导通,输出低电平;输入低电平时,PMOS导通、NMOS截止,输出高电平。这种结构的优势在于静态功耗极低(只在开关瞬间有动态电流),且输出摆幅大(接近电源电压),抗干扰能力强。基于反相器,可构建与门、或门、触发器等逻辑单元,进而组成微处理器、存储器(如DRAM、Flash)、FPGA等复杂数字芯片。例如,CPU中的数十亿个晶体管均为MOSFET,通过高频开关实现数据运算与存储;手机中的基带芯片、图像传感器也依赖MOSFET的高集成度与低功耗特性,满足便携设备的续航需求。此外,MOSFET的高输入阻抗还使其适合作为数字电路的输入缓冲器,避免信号衰减。微盟配套电源芯片与瑞阳微 MOSFET 协同,提升智能家电运行效率。有什么MOS代理商

MOSFET的动态特性测试聚焦于开关过程中的参数变化,直接关系到高频应用中的开关损耗与电磁兼容性(EMC)。动态特性测试主要包括上升时间tr、下降时间tf、开通延迟td(on)与关断延迟td(off)的测量,需使用示波器与脉冲发生器搭建测试电路:脉冲发生器提供栅极驱动信号,示波器同步测量Vgs、Vds与Id的波形。

上升时间tr是指Id从10%上升到90%的时间,下降时间tf是Id从90%下降到10%的时间,二者之和决定了开关速度(通常为几十至几百纳秒),速度越慢,开关损耗越大。开通延迟是指从驱动信号上升到10%到Id上升到10%的时间,关断延迟是驱动信号下降到90%到Id下降到90%的时间,延迟过大会影响电路的时序控制。此外,动态测试还需评估米勒平台(Vds下降过程中的平台期)的长度,米勒平台越长,栅极电荷Qg越大,驱动损耗越高。在高频应用中,需选择tr、tf小且Qg低的MOSFET,减少动态损耗。 有什么MOS代理商士兰微 SVF9N90F MOSFET 耐压值高,是高压电源设备的理想选择。

MOS 的工作原理重心是 “栅极电场调控沟道导电”,以增强型 N 沟道 MOS 为例,其工作过程分为三个关键阶段。截止状态:当栅极与源极之间电压 VGS=0 时,栅极无电场产生,源极与漏极之间的半导体区域为高阻态,无导电沟道,漏极电流 ID≈0,器件处于关断状态。导通状态:当 VGS 超过阈值电压 Vth(通常 1-4V)时,栅极电场穿透绝缘层作用于衬底,吸引衬底中的电子聚集在绝缘层下方,形成 N 型导电沟道,此时在漏极与源极之间施加正向电压 VDS,电子将从源极经沟道流向漏极,形成导通电流 ID。饱和状态:当 VDS 增大到一定值后,沟道在漏极一侧出现 “夹断”,但电场仍能推动电子越过夹断区,此时 ID 基本不受 VDS 影响,只随 VGS 增大而线性上升,适用于信号放大场景。整个过程中,栅极几乎不消耗电流(输入阻抗极高),只通过电压信号即可实现对大电流的精细控制。

MOS管(金属-氧化物-半导体场效应晶体管)分为n沟道MOS管(NMOS)和p沟道MOS管(PMOS),其工作原理主要基于半导体的导电特性以及电场对载流子的控制作用,以下从结构和工作机制方面进行介绍:结构基础NMOS:以一块掺杂浓度较低的P型硅半导体薄片作为衬底,在P型硅表面的两侧分别扩散两个高掺杂浓度的N+区,这两个N+区分别称为源极(S)和漏极(D),在源极和漏极之间的P型硅表面覆盖一层二氧化硅(SiO₂)绝缘层,在绝缘层上再淀积一层金属铝作为栅极(G)。

这样就形成了一个金属-氧化物-半导体结构,在源极和衬底之间以及漏极和衬底之间都形成了PN结。PMOS:与NMOS结构相反,PMOS的衬底是N型硅,源极和漏极是P+区,栅极同样是通过绝缘层与衬底隔开。工作机制以NMOS为例截止区:当栅极电压VGS小于阈值电压VTH时,在栅极下方的P型衬底表面形成的是耗尽层,没有反型层出现,源极和漏极之间没有导电沟道,此时即使在漏极和源极之间加上电压VDS,也只有非常小的反向饱和电流(漏电流)通过,MOS管处于截止状态,相当于开关断开。 瑞阳微自研 RS2300 系列 MOSFET 采用 SOT23 封装,体积小巧且功耗较低。

随着电子设备向“高频、高效、小型化、高可靠性”发展,MOSFET技术正朝着材料创新、结构优化与集成化三大方向突破。材料方面,传统硅基MOSFET的性能已接近物理极限,宽禁带半导体材料(如碳化硅SiC、氮化镓GaN)成为主流方向:SiCMOSFET的击穿电场强度是硅的10倍,导热系数更高,可实现更高的Vds、更低的Rds(on)和更快的开关速度,适用于新能源、航空航天等高压场景;GaNHEMT(异质结场效应晶体管)则在高频低压领域表现突出,可应用于5G基站、快充电源,实现更小体积与更高效率。结构优化方面,三维晶体管(如FinFET)通过立体沟道设计,解决了传统平面MOSFET在小尺寸下的短沟道效应,提升了集成度与开关速度,已成为CPU、GPU等高级芯片的主要点技术。集成化方面,功率MOSFET与驱动电路、保护电路集成的“智能功率模块(IPM)”,可简化电路设计,提高系统可靠性,频繁应用于家电、工业控制;而多芯片模块(MCM)则将多个MOSFET与其他器件封装在一起,进一步缩小体积,满足便携设备需求。未来,随着材料与工艺的进步,MOSFET将在能效、频率与集成度上持续突破,支撑新一代电子技术的发展士兰微 SVF20N60F MOSFET 耐压性出色,是工业控制设备的选择。有什么MOS代理商

士兰微 SGT 系列 MOSFET 适配逆变器,满足高功率输出应用需求。有什么MOS代理商

MOS 的技术发展始终围绕 “缩尺寸、提性能、降功耗” 三大目标,历经半个多世纪的持续迭代。20 世纪 60 年代初,首代平面型 MOS 诞生,采用铝栅极与二氧化硅绝缘层,工艺节点只微米级,开关速度与集成度较低;70 年代,多晶硅栅极替代铝栅极,结合离子注入掺杂技术,阈值电压控制精度提升,推动 MOS 进入大规模集成电路应用;80 年代,沟槽型 MOS 问世,通过干法刻蚀技术构建垂直沟道,导通电阻降低 50% 以上,适配中等功率场景;90 年代至 21 世纪初,工艺节点进入纳米级(90nm-45nm),高 k 介质材料(如 HfO₂)替代传统二氧化硅,解决了绝缘层漏电问题,同时铜互连技术提升芯片散热与信号传输效率;2010 年后,FinFET(鳍式场效应晶体管)成为主流,3D 栅极结构大幅增强对沟道的控制能力,突破平面 MOS 的短沟道效应瓶颈,支撑 14nm-3nm 先进制程芯片量产;如今,GAA(全环绕栅极)技术正在崛起,进一步缩窄沟道尺寸,为 1nm 及以下制程奠定基础。有什么MOS代理商