商机详情 -

西安SD分析仪厂家

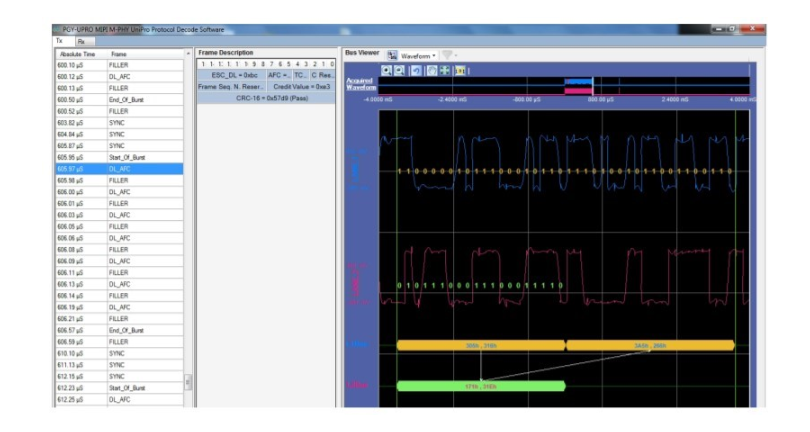

逻辑分析仪也是必不可少的。逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,主要的作用在于时序判定。逻辑分析仪与示波器不同,它不能显示连续的模拟量波形,而只显示高低两种电平状态(逻辑1和0)。在设置了参考电压后,逻辑分析仪将采集到的信号与电压比较器比较,高于参考电压的为逻辑1,低于参考电压的为逻辑0。这样就可以将被测信号以时间顺序显示为连续的高低电平波形,便于使用者进行分析和调试。使用逻辑分析仪,可以方便地设置信号触发条件开始采样,分析多路信号的时序,捕获信号的干扰毛刺,也可以按照规则对电平序列进行解码,完成通信协议分析。图1逻辑分析仪根据其硬件设备的功能和复杂程度,主要分为式(单机型)逻辑分析仪和基于电脑(PC-Base)的虚拟逻辑分析仪两大类。式逻辑分析仪是将所有的软件,硬件整合在一台仪器中,使用方便。虚拟逻辑分析仪则需要结合电脑使用,利用PC强大的计算和显示功能,完成数据处理和显示等工作。专业逻辑分析仪,通常具有数量众多的采样通道,超快的采样速度和大容量的存储深度,但昂贵的价格也不是个人所能承受的。作为工程师手头常备的开发工具,目前有许多入门级的逻辑分析仪设计。SD协议分析仪/训练器厂家那家好?找欧奥!西安SD分析仪厂家

没有额外的被测设备)的一小段时间内,可以自动:定位每个通道上的建立/保持窗口。针对尽可能宽的数据有效窗口调整阈电压设置。眼定位是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。眼定位概要:对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置佳采样位置。为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。例如,如果选择盒1上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒1时钟上的上升沿。盒1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。要构建眼定位显示,需要将无数张这样的“照片”堆叠在彼此的顶端。每张“照片”都在T=0时对齐,此时将达到活动时钟沿。照片拍自上升沿还是下降沿并没有关系;它们会在T=0时对齐。构建显示后。云浮逻辑分析仪收费分析仪/训练器怎么选?找欧奥!

会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器。

以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。除非已在触发序列中使用了它们。一般情况下,如果可能的话,应使用发生计数器代替全局计数器,原因是发生计数器的用法比较简单,而且全局计数器的数量有限。定时器:定时器用于检查事件之间消耗的时间。例如,如果想在出现一个时钟沿后的500ns内出现另一个时钟沿的情况下引发触发,请使用定时器。使用定时器时要记住的关键一点是:先启动定时器,然后再对其进行测试。换句话说,定时器无法自动启动。设置定时器的关键是确定在何种情况下进行启动和测试。存储限定:存储限定用于确定应该存储(即,存入内存)还是丢弃已获得的样本。这可以避免不需要的样本占用逻辑分析仪内存。设置存储限定简单的方法是设置“默认存储”。默认存储表示“如果未经序列步骤指定,则进行存储”。例如,可能只想在ADDR的范围为1000到2000时存储样本,那么就应将“默认存储”设置为:ADDRInRange1000to2000默认情况下,“默认存储”设置为存储所有已获得的样本。也可以将“默认存储”设置为不存储任何样本,这意味着除非某序列步骤覆盖该默认存储,否则将不存储任何样本。分析仪厂家哪家好?欧奥电子好!

输入接口单元能够提供与被测设备接口相同的电气条件和物理条件。数据以串行方式透明地通过切换器直接进入串-并变换器。数据在串-并变换器中建立同步,且由串行变换为并行,同时还进行差错检验。由此进入捕获存储器、触发器和收发信分析器。捕获存储器将输入的数据收录下来,进行再生显示、详细检验和其他的脱线处理。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。触发器则根据设定的比特序列、差错计数、调制解调器的控制信号和外部输入等各种触发因素,迅速地进行数据分析和故障切离。收发信分析器以协议(通常有BSC、HDLC、SDLC、X.25和X.75等)为基准来分析和检验数据,且以“助记符”的形式由示波器显示出来。SMI(MDIO)协议分析仪/训练器找欧奥!惠州SD分析仪品牌

SD协议分析仪/训练器找欧奥!西安SD分析仪厂家

在跳变定时中,每个序列步骤只有2个分支。在跳变时序中,只有一个全局计数器可用。跳变时序需要有时间标签才能重建数据。通过将时间标签与内存中的测量数据交叉可存储时间标签。默认情况下,分析仪将查找为逻辑分析仪模块定义的所有总线/信号上的转变。但是,为增加可用内存深度和采集时间,可以在高级触发中选择不存储某些总线/信号转变(如将无用信息添加到测量中的时钟或选冲信号)。运行测量时,无论总线/信号是否定义或是否分配给逻辑分析仪通道,都将在所有这些通道上采集数据。在跳变时序模式中,如果定义的总线/信号(未排除的)上存在转变,将保存采集的样本。运行跳变时序测量后。如果为以前未分配的逻辑分析仪通道定义新的总线/信号,那么将显示在这些通道上采集的数据,但是不可能存储这些总线/信号上的所有转变;显示的数据好似新的总线/信号在运行测量前就已经被排除了。在跳变时序中,不需要预先存储数据(触发前获得的样本)。因此,与状态模式非常相似的是,触发位置(起始/中心/结束)表明触发后样本占用内存的百分比。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。西安SD分析仪厂家