商机详情 -

广州分析仪

将内存深度设置为值的一半(或更小)将返回Pod。在状态采样模式中,在选择了高速状态模式采样选项的情况下,会将一个Pod对保留用于时间标签存储。在定时采样模式中,在选择了跳变/存储限定定时模式采样选项的情况下:选择了小采样周期时,会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。SDIO协议分析仪/训练器找欧奥!广州分析仪

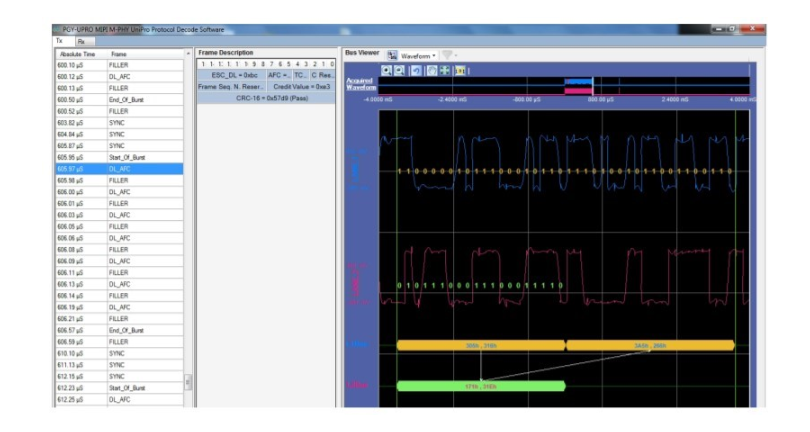

欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。逻辑分析仪也是必不可少的。逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,主要的作用在于时序判定。逻辑分析仪与示波器不同,它不能显示连续的模拟量波形,而只显示高低两种电平状态(逻辑1和0)。在设置了参考电压后,逻辑分析仪将采集到的信号与电压比较器比较,高于参考电压的为逻辑1,低于参考电压的为逻辑0。这样就可以将被测信号以时间顺序显示为连续的高低电平波形,便于使用者进行分析和调试。使用逻辑分析仪,可以方便地设置信号触发条件开始采样,分析多路信号的时序,捕获信号的干扰毛刺,也可以按照规则对电平序列进行解码,完成通信协议分析。成都RFFE分析仪QSPI协议分析仪/训练器找欧奥!

序列步骤存储限定意味着在某个特定的序列步骤内只存储特定的样本。这意味着在使用GoTo(转到)或Trigger。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。触发)操作离开此序列步骤之前。应用该存储限定。如果要为每个序列步骤应用不同的存储限定,该存储限定很有用。例如,可能不希望在ADDR=1000之前存储任何样本,而对于其余的测量,只存储ADDR在1000到2000范围之内的样本。设置序列步骤存储还需要再使用一条分支指令。例如,在查找DATA=005E时,如果只希望存储ADDR在5000到6FFF范围之内的样本,某些情况下可使用以下序列步骤:。这表示“立即存储内存中新获得的样本”。而不表示“从现在起,开始存储”。应当注意。

没有额外的被测设备)的一小段时间内,可以自动:定位每个通道上的建立/保持窗口。针对尽可能宽的数据有效窗口调整阈电压设置。眼定位是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。眼定位概要:对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置佳采样位置。为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。例如,如果选择盒1上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒1时钟上的上升沿。盒1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。要构建眼定位显示,需要将无数张这样的“照片”堆叠在彼此的顶端。每张“照片”都在T=0时对齐,此时将达到活动时钟沿。照片拍自上升沿还是下降沿并没有关系;它们会在T=0时对齐。构建显示后。UniPro协议分析仪/训练器找欧奥!

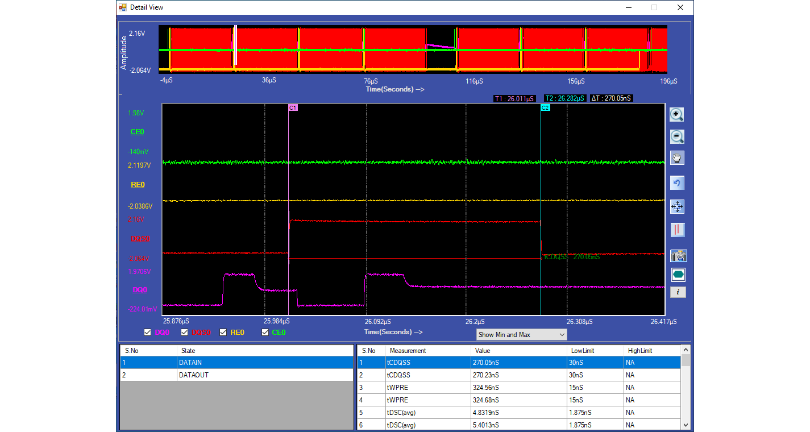

逻辑分析仪使用标配的电源适配器供电,并按下电源键。用USB线将仪器与PC机相连,并打开软件,观察软件界面上方是否有“在线”。将IIC协议(幅值,频率为50KHz)接入,使用测量线PODA中的A1接SCL,A0接SDA,并确保信号地线已经接好。二、IIC总线设置1、点击总线名称可以修改总线名称,建议不要有重复;2、总线名称好与通道意义相关;3、不要增加相同的总线,软件会将它们过滤掉;4、不要增加没有通道的总线;5、没用的总线及时删除,看起来更简洁。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。设置效果如图1所示:图1IIC通道开启三、IIC采样参数设置1、采样模式:同步异步的区别,同步采样优势。SPMl协议分析仪/训练器找欧奥!宁波UART分析仪报价

RFFE协议分析仪/训练器找欧奥!广州分析仪

系统的电流负载能力一般在几个KΩ以上,分流效应对系统的影响一般可以忽略,现在流行的几种长逻辑分析仪探头的阻抗一般在20~200KΩ之间。b、探头的容性负载:容性负载就是探头接入系统时,探头的等效电容,这个值一般在1~30PF之间,在高速系统中,容性负载对电路的影响远远于阻性负载,如果这个值太,将会直接影响整个系统中的信号"沿"的形状改变整个电路的性质,改变逻辑分析仪对系统观测的实时性,导致我们看到的并不是系统原有的特性。c、探头的易用性:是指探头接入系统时的难易程度,随着芯片封装的密度越来越高,出现了BGA、QFP、TQFP、PLCC、SOP等各种各样的封装形式,IC的脚间距小的已达到,要很好的将信号引出,特别是BGA封装,确实有困难,并且分立器件的尺寸也越来越小,典型的已达到×。d、与现有电路板上的调试部分的兼容性。6、系统的开放性:随着数据共享的呼声越来越高,我们所使用的系统的开放性就越来越重要,逻辑分析仪的操作系统也由过去的系统发展到使用Windows介面,这样我们在使用时很方便。小结如果在你的工作中有数字逻辑信号,你就有机会使用逻辑分析仪。因此应选好一种逻辑分析仪,既符合所用的功能,又不太超越所需的功能。广州分析仪