商机详情 -

天津FPGA开发硬件开发供应商

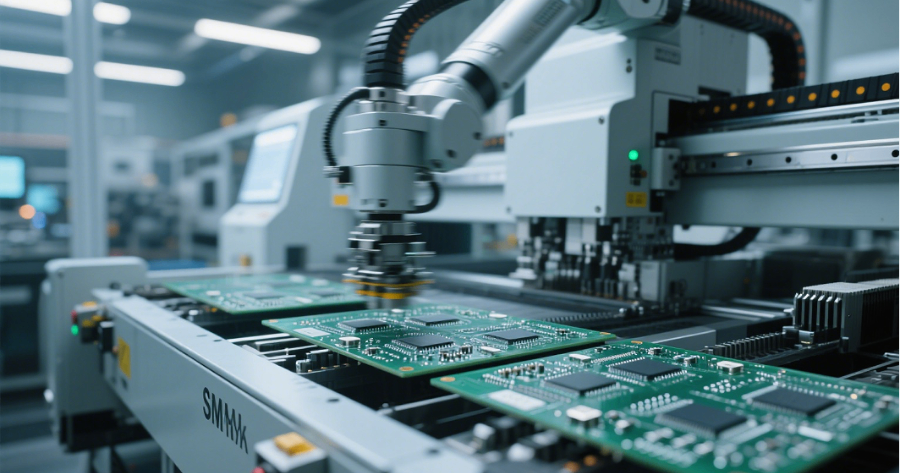

随着 5G、未来 6G 等通信技术的发展,数据流量呈爆发式增长,通信设备硬件开发必须满足高速数据传输的严苛要求。在硬件架构设计上,采用高速串行接口(如 SerDes)和多通道并行传输技术,提升数据传输速率。例如,5G 基站的基带处理单元与射频单元之间,通过高速光纤连接,实现海量数据的实时传输。同时,优化信号处理电路,采用先进的调制解调技术和信道编码技术,提高数据传输的准确性和抗干扰能力。在元器件选型方面,选用高速、低延迟的芯片和存储器件,如高速 FPGA、DDR5 内存等,满足数据处理和缓存需求。此外,通信设备还需具备强大的散热能力,以保证高速运行时的稳定性。例如,数据中心的交换机采用液冷散热系统,确保设备在高负载下持续稳定工作。只有不断突破技术瓶颈,满足高速数据传输需求,通信设备硬件才能支撑起智能互联时代的海量数据交互。长鸿华晟将电路设计转换成 PCB 布局时,精心规划元器件放置与线路布线。天津FPGA开发硬件开发供应商

汽车电子系统直接关系到行车安全和驾乘体验,其硬件开发必须满足极高的安全性和稳定性标准。以汽车的电子控制单元(ECU)为例,它负责发动机控制、刹车系统调节等关键功能,一旦出现故障可能引发严重后果。因此,汽车电子硬件开发遵循严格的功能安全标准,如 ISO 26262,要求对硬件设计进行的失效模式与影响分析(FMEA),识别潜在故障点并采取冗余设计、故障检测等措施。在传感器开发方面,用于自动驾驶的毫米波雷达、激光雷达,不仅要具备高精度的探测能力,还要能在高温、低温、潮湿等恶劣环境下稳定工作,其硬件设计需采用高可靠性的元器件和防护等级高的封装工艺。此外,汽车电子系统还面临复杂的电磁环境干扰,硬件开发需进行严格的电磁兼容性(EMC)设计,确保各电子模块之间互不干扰。只有满足这些严苛要求,汽车电子硬件才能为车辆的安全运行和智能化发展提供坚实保障。天津FPGA开发硬件开发供应商长鸿华晟通过优化供电系统,如使用高效电源等方式,提升硬件稳定性和性能。

硬件开发项目从立项到量产,每个环节都涉及成本支出,因此成本预算需贯穿项目始终。在项目前期,需对研发成本进行估算,包括人力成本、设备采购成本、原材料成本等。例如,开发一款智能音箱,要预估工程师的薪酬、开发工具的购置费用以及芯片、扬声器等元器件的采购成本。设计阶段,通过优化电路设计、合理选型元器件来控制成本,避免过度设计造成浪费。量产阶段,需关注生产成本,如生产工艺的复杂度、生产线的自动化程度都会影响成本。此外,还要考虑售后成本,包括维修、退换货等费用。通过建立的成本预算体系,对项目各阶段的成本进行监控和调整,确保项目在预算范围内完成。同时,成本预算也能为产品定价提供依据,帮助企业在市场竞争中制定合理的价格策略。

硬件开发不是单纯地追求功能强大,还需要在功能实现、成本控制和生产可行性之间找到平衡。在功能实现方面,要确保产品能够满足用户的需求和使用场景;在成本控制上,需要合理选择元器件,优化设计方案,避免不必要的成本浪费。例如,在开发一款家用智能摄像头时,既要保证其具备高清拍摄、移动侦测、云端存储等功能,又要考虑到成本因素。如果选择过于昂贵的芯片和传感器,虽然能提升产品性能,但会导致成本过高,影响产品的市场定价和竞争力。同时,硬件开发方案还需要考虑生产可行性,设计要符合生产工艺要求,便于大规模生产。比如,PCB 设计的复杂度要适中,避免因设计过于复杂导致生产难度增加,良品率降低。只有兼顾这三个方面,才能开发出既实用又具有市场竞争力的硬件产品。长鸿华晟的硬件开发团队凭借深厚的专业知识,把握产品的功能与性能需求,为硬件产品奠定基础。

硬件开发从设计图纸到实际产品,原型制作是不可或缺的环节,它能够直观验证设计思路的可行性,发现潜在问题并及时优化。在原型制作阶段,工程师通常采用快速成型技术,如 3D 打印制作机械外壳模型,验证产品的外形尺寸和装配关系;通过手工焊接或 PCB 打样制作电子电路原型,测试电路功能和性能。例如,在开发一款新型智能门锁时,制作原型可以验证指纹识别模块的灵敏度、无线通信模块的连接稳定性以及机械锁芯的可靠性。如果在原型测试中发现指纹识别速度慢,工程师可以分析是传感器选型问题还是算法优化不足;若无线通信不稳定,可检查天线设计和信号处理电路。通过原型制作,将抽象的设计转化为实物,不仅能帮助团队成员更清晰地理解产品架构,还能提前暴露设计缺陷,避免在大规模生产阶段出现问题,降低开发风险,缩短产品上市周期。长鸿华晟的单板硬件详细设计报告重点突出,对逻辑框图、物料清单等内容详细说明。山东摄像头开发硬件开发平台

长鸿华晟在调试过程中,保持平和心态,通过比较和分析逐步排除问题。天津FPGA开发硬件开发供应商

时钟电路为硬件系统提供基准时钟信号,如同整个系统的 “心脏起搏器”,控制着各个模块的运行节奏,是系统实现同步运行的基础。在数字电路中,时钟信号决定了数据的传输速率和处理周期,时钟信号的稳定性和准确性直接影响系统性能。常见的时钟电路包括晶体振荡器、锁相环(PLL)等。晶体振荡器利用石英晶体的压电效应产生稳定的振荡信号,为系统提供基本时钟频率;锁相环则可对时钟信号进行倍频或分频处理,满足不同模块对时钟频率的需求。在多核处理器的硬件开发中,精确的时钟同步至关重要,若各的时钟信号存在微小偏差,会导致数据处理错误和系统不稳定。此外,在通信设备中,时钟电路的抖动(Jitter)指标直接影响信号传输的准确性,抖动过大可能导致数据误码率升高。因此,在硬件开发中,需精心设计时钟电路,合理选择时钟芯片和布局布线,减少时钟信号的干扰和损耗,确保整个硬件系统能够稳定、同步地运行。天津FPGA开发硬件开发供应商