商机详情 -

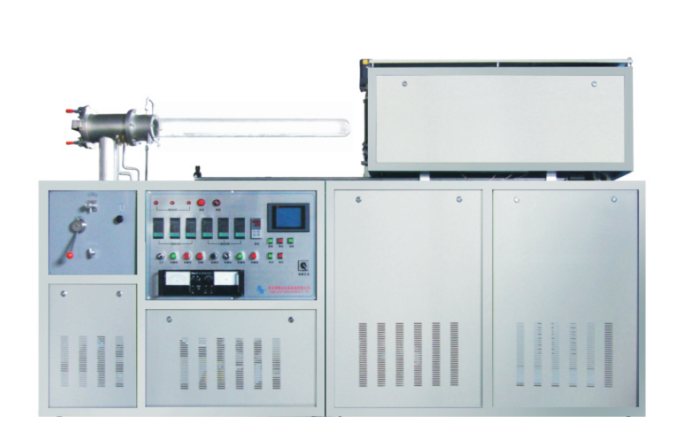

长沙8英寸管式炉掺杂POLY工艺

管式炉在硅外延生长中通过化学气相沉积(CVD)实现单晶层的可控生长,典型工艺参数为温度1100℃-1200℃、压力100-500Torr,硅源气体(SiH₄或SiCl₄)流量50-500sccm。外延层的晶体质量受衬底预处理、气体纯度和温度梯度影响明显。例如,在碳化硅(SiC)外延中,需在800℃下用氢气刻蚀去除衬底表面缺陷,随后在1500℃通入丙烷(C₃H₈)和硅烷(SiH₄)实现同质外延,生长速率控制在1-3μm/h以减少位错密度5。对于化合物半导体如氮化镓(GaN),管式炉需在高温(1000℃-1100℃)和氨气(NH₃)气氛下进行异质外延。通过调节NH₃与三甲基镓(TMGa)的流量比(100:1至500:1),可精确控制GaN层的掺杂类型(n型或p型)和载流子浓度(10¹⁶-10¹⁹cm⁻³)。此外,采用梯度降温(5℃/min)可缓解外延层与衬底间的热应力,降低裂纹风险。管式炉可通入多种气体(氮气、氢气等),实现惰性或还原性气氛下的化学反应。长沙8英寸管式炉掺杂POLY工艺

管式炉的安全系统包括:①过温保护(超过设定温度10℃时自动切断电源);②气体泄漏检测(半导体传感器响应时间<5秒),并联动关闭进气阀;③紧急排气系统(流量>1000L/min),可在30秒内排空炉内有害气体(如PH₃、B₂H₆)。操作人员需佩戴耐酸碱手套、护目镜和防毒面具,并在通风橱内进行有毒气体操作。对于易燃易爆工艺(如氢气退火),管式炉配备防爆门(爆破压力1-2bar)和火焰探测器,一旦检测到异常燃烧,立即启动惰性气体(N₂)吹扫程序。北京赛瑞达管式炉掺杂POLY工艺适用于半导体研发与生产,助力技术创新,欢迎联系获取支持!

管式炉精确控制的氧化层厚度和质量,直接影响到蚀刻过程中掩蔽的效果。如果氧化层厚度不均匀或存在缺陷,可能会导致蚀刻过程中出现过刻蚀或蚀刻不足的情况,影响电路结构的精确性。同样,扩散工艺形成的 P - N 结等结构,也需要在蚀刻过程中进行精确的保护和塑造。管式炉对扩散工艺参数的精确控制,确保了在蚀刻时能够准确地去除不需要的材料,形成符合设计要求的精确电路结构。而且,由于管式炉能够保证工艺的稳定性和一致性,使得每一片硅片在进入蚀刻工艺时都具有相似的初始条件,从而提高了蚀刻工艺的可重复性和产品的良品率,为半导体器件的大规模生产提供了有力支持。

在半导体CVD工艺中,管式炉通过热分解或化学反应在衬底表面沉积薄膜。例如,生长二氧化硅(SiO₂)绝缘层时,炉内通入硅烷(SiH₄)和氧气,在900°C下反应生成均匀薄膜。管式炉的线性温度梯度设计可优化气体流动,减少湍流导致的膜厚不均。此外,通过调节气体流量比(如TEOS/O₂),可控制薄膜的介电常数和应力。行业趋势显示,低压CVD(LPCVD)管式炉正逐步兼容更大尺寸晶圆(8英寸至12英寸),并集成原位监测模块(如激光干涉仪)以提升良率。

由于化合物半导体对生长环境的要求极为苛刻,管式炉所具备的精确温度控制、稳定的气体流量控制以及高纯度的炉内环境,成为了保障外延层高质量生长的关键要素。在碳化硅外延生长过程中,管式炉需要将温度精确控制在 1500℃ - 1700℃的高温区间,并且要保证温度波动极小,以确保碳化硅原子能够按照特定的晶体结构进行有序沉积。同时,通过精确调节反应气体的流量和比例,如硅烷和丙烷等气体的流量控制,能够精确控制外延层的掺杂浓度和晶体质量。赛瑞达管式炉优化气流,实现半导体 CVD 薄膜高品沉积,等您来电!苏州一体化管式炉LTO工艺

高效冷冷却系统,缩短设备冷却时间,提升生产效率,了解更多!长沙8英寸管式炉掺杂POLY工艺

管式炉在碳化硅(SiC)和氮化镓(GaN)制造中面临高温(1500℃以上)和强腐蚀气氛(如HCl)的挑战。以SiC外延为例,需采用石墨加热元件和碳化硅涂层石英管,耐受1600℃高温和HCl气体腐蚀。工艺参数为:温度1500℃-1600℃,压力50-100Torr,硅源为硅烷(SiH₄),碳源为丙烷(C₃H₈),生长速率1-2μm/h。对于GaN基LED制造,管式炉需在1050℃下进行p型掺杂(Mg源为Cp₂Mg),并通过氨气(NH₃)流量控制(500-2000sccm)实现载流子浓度(10¹⁹cm⁻³)的精确调控。采用远程等离子体源(RPS)可将Mg***效率提升至90%以上,相比传统退火工艺明显降低能耗。长沙8英寸管式炉掺杂POLY工艺