商机详情 -

东莞KDS有源晶振购买

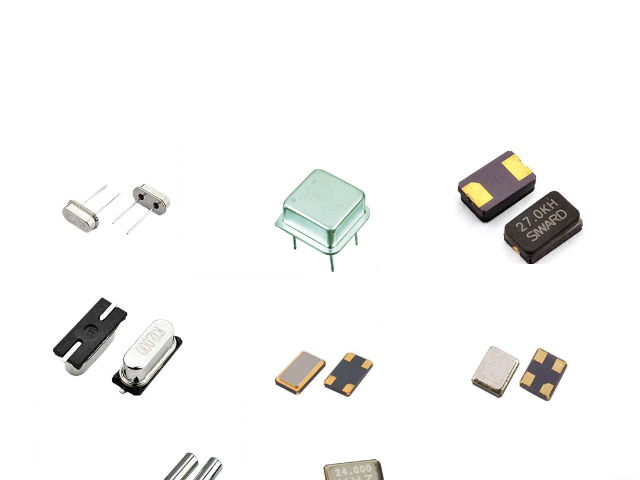

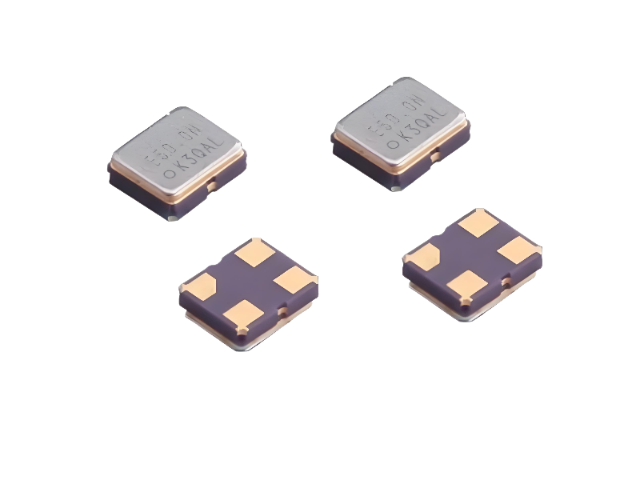

有源晶振的便捷连接特性,从接口、封装到接线逻辑简化设备组装流程,大幅降低操作难度与出错风险。首先是标准化接口设计,其普遍支持 CMOS、LVDS、ECL 等行业通用输出接口,可直接与 MCU、FPGA、射频芯片等器件的时钟引脚对接 —— 无需像部分特殊时钟模块那样,额外设计接口转换电路或焊接转接座,组装时只需按引脚定义对应焊接,避免因接口不兼容导致的线路修改或元件返工,尤其适合中小批量设备的快速组装。其次是适配自动化组装的封装形式,主流有源晶振采用 SMT(表面贴装技术)封装,如 3225(3.2mm×2.5mm)、2520(2.5mm×2.0mm)等规格,引脚布局规整且间距统一(常见 0.5mm/0.8mm 引脚间距),可直接通过贴片机定位焊接,无需手工插装 —— 相比传统 DIP(双列直插)封装的晶振,省去了穿孔焊接的繁琐步骤,不仅将单颗晶振的组装时间从 30 秒缩短至 5 秒,还避免了手工焊接时可能出现的虚焊、错焊问题,适配消费电子、工业模块等自动化生产线的组装需求。连接有源晶振后,设备无需再配置复杂的信号调理电路。东莞KDS有源晶振购买

有源晶振还集成了电源稳压单元与滤波电路。稳压单元可稳定供电电压,避免电压波动对内部电路工作的干扰;滤波电路则能滤除供电链路中的纹波噪声及外部电磁辐射带来的杂波。这种一体化设计减少了外部元件引入的寄生参数(如寄生电容、电感),避免了外部电路与晶振之间的信号干扰,无需额外搭配驱动电路即可直接输出频率范围 1MHz-1GHz 的纯净时钟信号。正因如此,有源晶振在 5G 通信基站、工业 PLC、高精度医疗设备等对时钟稳定性要求严苛的场景中广泛应用,为系统时序控制提供可靠保障。佛山NDK有源晶振作用有源晶振的低噪声输出,满足敏感电子设备的使用要求。

对比传统无源晶振,其无温度补偿设计,在 - 40℃~85℃温变下稳定度常突破 100ppm,无法满足设备需求;而有源晶振的补偿机制还搭配密封陶瓷封装,能隔绝外部温变对内部电路的快速冲击,避免温度骤升骤降导致的瞬时频率波动。这种稳定度在多场景中至关重要:户外物联网网关需耐受 - 30℃~70℃昼夜温差,15-50ppm 稳定度可避免时钟漂移导致的 LoRa/NB-IoT 通信断连;工业烤箱控制模块在 0℃~200℃(需高温型有源晶振)环境中,该稳定度能确保加热时序精确,避免温差超 ±1℃;汽车电子(如车载雷达)在 - 40℃~125℃工况下,也依赖此稳定度保障信号处理时序,防止探测精度偏差。此外,有源晶振出厂前会经过 - 55℃~125℃温循测试,筛选出稳定度达标产品,确保实际应用中持续符合 15-50ppm 的性能要求。

面对工业车间、消费电子主板的电磁辐射(EMI)干扰,有源晶振内置 EMC 抑制电路与屏蔽封装:电路中的共模电感可抵消外部电磁杂波产生的共模电流,差分输出架构(如 LVDS 接口)能将电磁干扰对信号的影响降低 80% 以上,配合密封陶瓷封装隔绝外部辐射,使输出信号的相位噪声在电磁干扰环境下仍稳定在 - 120dBc/Hz(1kHz 偏移),避免杂波导致的信号失真。此外,内置温度补偿电路还能减少温变干扰:环境温度波动会导致晶体谐振参数变化,进而影响信号稳定性,而有源晶振的热敏电阻与补偿电路可实时修正频率偏差,在 - 40℃~85℃温变下将干扰引发的频率漂移控制在 ±5ppm 内。例如工业变频器附近的 PLC 设备,受电磁与温变双重干扰,有源晶振的内置电路可确保时钟信号无异常,避免 PLC 逻辑指令误触发,相比无内置防护的无源晶振,抗干扰能力提升 3-5 倍,为设备稳定运行提供保障。有源晶振内置振荡器和晶体管,能直接输出高质量时钟信号。

在高精度场景中,时钟信号的噪声会直接影响系统性能,而有源晶振的低噪声优势能有效规避这一问题。从设计来看,有源晶振多采用低噪声晶体管架构,如差分对管设计,可抑制共模噪声干扰,同时通过负反馈电路控制信号放大过程,避免放大环节引入额外噪声,其相位噪声指标通常能达到 1kHz 偏移时低于 - 130dBc/Hz,远优于无源晶振搭配外部电路的噪声表现。对于 5G 通信基站这类高精度场景,信号解调对时钟相位稳定性要求极高,若时钟噪声过大,会导致星座图偏移,增加误码率。有源晶振内置的高精度晶体谐振器,能减少温度、电压波动引发的频率漂移,配合电源滤波单元滤除供电链路的纹波噪声,确保输出时钟信号的相位抖动控制在 1ps 以内,保障信号解调精度。高精度场景下,有源晶振的低噪声优势表现十分突出。西安YXC有源晶振多少钱

有源晶振无需滤波电路辅助,直接输出符合要求的时钟信号。东莞KDS有源晶振购买

有源晶振能从电路设计全流程减少工程师的操作步骤,在于其集成化特性替代了传统方案的多环节设计,直接压缩开发周期,尤其适配消费电子、物联网模块等快迭代领域的需求。在原理图设计阶段,传统无源晶振需工程师单独设计振荡电路(如 CMOS 反相器振荡架构)、匹配负载电容(12pF-22pF)、反馈电阻(1MΩ-10MΩ),若驱动能力不足还需增加驱动芯片(如 74HC04),只时钟部分就需绘制 10 余个元件的连接逻辑,步骤繁琐且易因引脚错连导致设计失效。而有源晶振内置振荡、放大、稳压功能,原理图只需设计 2-3 个引脚(电源正、地、信号输出)的简单回路,绘制步骤减少 70% 以上,且无需担心振荡电路拓扑错误,降低设计返工率。东莞KDS有源晶振购买