商机详情 -

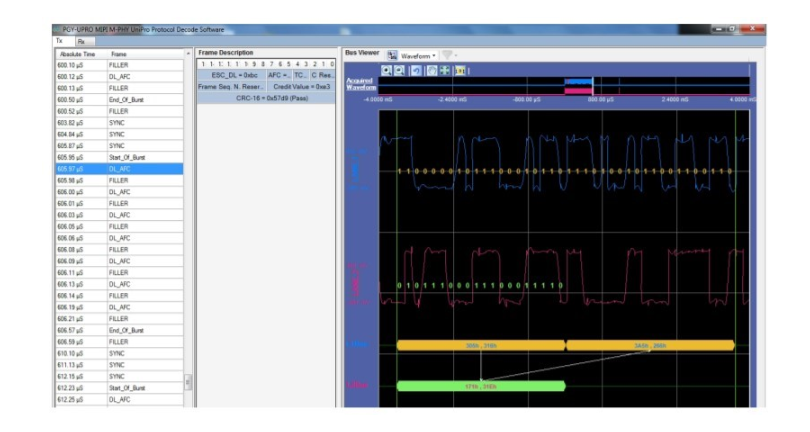

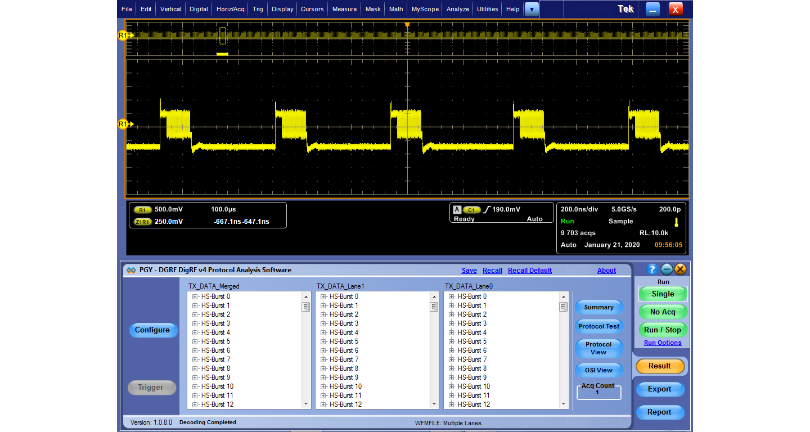

重庆RFFE分析仪收费

的发生时间。当需要象接收芯片一样基于时钟边沿,捕获总线中的信息时。接收芯片基于时钟边沿判断总线上的地址、命令和数据。逻辑分析仪象一个侦听器。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。捕获总线上传输的这些信息,并把需要的信息存入存储器。可设置触发条件。捕获需要关注的或出问题的总线上的信息,据此可了解协议或软件执行的情况。上面已经简短讨论了逻辑分析仪的一些用法,现在,让我们更详细地了解一下有关逻辑分析仪的概念。到目前为止,我们已经很地使用了“逻辑分析仪”这一术语。实际上,多数逻辑分析仪中都包含两个分析仪。1.定时分析仪:定时分析仪是逻辑分析仪的一部分,它与示波器相似。事实上。训练器厂家哪家强?欧奥就是强!重庆RFFE分析仪收费

多总线上的数据有效窗口小于总线时间周期的一半。要精确采集总线上的数据,需符合以下条件:逻辑分析仪的建立/保持时间必须在数据有效窗口内。图12有效采集窗口由于与总线时钟有关的数据有效窗口的位置根据总线类型的不同而有所变化,因此逻辑分析仪的建立/保持窗口的位置在数据有效窗口中必须是可调整的(相对于采样时钟,且具有较高分辨率)。例如:图13调整采样位置为了将建立/保持窗口(采样位置)放置在数据有效窗口内,逻辑分析仪可在每次采样输入时调整延迟(以定位每个通道的建立/保持窗口)。如果可以在单个通道上调整采样位置,可以使逻辑分析仪的建立/保持窗口变小,因为可以校准由探头电缆和逻辑分析仪的内部电路板跟踪引起的偏移效应,而且还可以看到逻辑分析仪的内部采样电路的建立/保持要求。但是,手动定位每个通道的建立/保持窗口需要花费量时间。对于被测设备中的每个信号和每个逻辑分析仪通道来说,必须测量与总线时钟(带有示波器)相关的数据有效窗口,重复定位建立/保持窗口并运行测量以查看逻辑分析仪是否正确采集数据,后再将建立/保持窗口定位在错误采集数据的位置之间。使用具有眼定位(eyefinder)功能的逻辑分析仪,在手动调整。宁波EMMC分析仪售价RFFE协议分析仪/训练器找欧奥!

模拟器在执行模拟功能时使用。大容量存储器用于保存监视器和模拟器的设定条件清单、模拟过程的程序和捕获存储器收录的数据等,主控制器用于控制协议分析仪各个组成部分的动作,并且进行实时调节和协调,对各部分进行初始化。协议分析仪功能协议分析仪的基本功能有:①监视功能:将协议分析仪连接在数据通信系统上,在不影响系统运行的情况下,从线路上取出所发送的数据和接收的数据,进行数据的存储、显示和分析。②模拟功能,将协议分析仪直接与被测设备(数据终端设备或主计算机)连接,按照预先设置的程序,同被测设备通信,进行数据的发送、接收数据的判断和应答数据的判断,检验被测设备协议实现的正确性。协议分析仪组成协议分析仪的标准框图如图1所示,由输入接口单元、切换器、串-并变换器、捕获存储器、触发器、收发信分析器、显示器、模拟器、大容量存储器和主控制器等部分组成。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。

系统的电流负载能力一般在几个KΩ以上,分流效应对系统的影响一般可以忽略,现在流行的几种长逻辑分析仪探头的阻抗一般在20~200KΩ之间。b、探头的容性负载:容性负载就是探头接入系统时,探头的等效电容,这个值一般在1~30PF之间,在高速系统中,容性负载对电路的影响远远于阻性负载,如果这个值太,将会直接影响整个系统中的信号"沿"的形状改变整个电路的性质,改变逻辑分析仪对系统观测的实时性,导致我们看到的并不是系统原有的特性。c、探头的易用性:是指探头接入系统时的难易程度,随着芯片封装的密度越来越高,出现了BGA、QFP、TQFP、PLCC、SOP等各种各样的封装形式,IC的脚间距小的已达到,要很好的将信号引出,特别是BGA封装,确实有困难,并且分立器件的尺寸也越来越小,典型的已达到×。d、与现有电路板上的调试部分的兼容性。6、系统的开放性:随着数据共享的呼声越来越高,我们所使用的系统的开放性就越来越重要,逻辑分析仪的操作系统也由过去的系统发展到使用Windows介面,这样我们在使用时很方便。小结如果在你的工作中有数字逻辑信号,你就有机会使用逻辑分析仪。因此应选好一种逻辑分析仪,既符合所用的功能,又不太超越所需的功能。SSIC协议分析仪/训练器找欧奥!

DampedResistorProbing),电阻匹配探测(ResistiveDividerProbing)。短线探测会增加电容负载。举例:探头电容负载是,连接短线是50欧姆微带线(C=3pF/in),长度1英寸。则整个探头的电容负载是,这个短线是电容负载的主要部分。被测系统可容忍的负载电容是多少呢?需要参考被测电路的系统上升时间,一般规则:短线的电气长度<>PCB传输延迟:150ps/in系统上升时间:500ps则电气长度:则短线长度:(100ps)/(150ps/in)=。如果没法减小短线长度,可以试着用阻尼电阻探测的方式。阻尼电阻有2个作用:隔离来自短线的电容,消减来自短线的反射。图25阻尼电阻探测方式阻尼电阻阻值小的一般规则:目标阻抗的。如果探测环境需要更长的连线,这时候可考虑电阻匹配探测,即在探头尖处附加一个匹配电阻,消除连线的反射。匹配电阻的阻值与连线传输线的阻抗一样即可,但需要考虑信号的衰减。图26电阻匹配探测方式逻辑分析仪的探头主要有3种类型:提前设计型;事后考虑型;定制型。图27逻辑分析仪的探头类型小结:逻辑分析仪探头是逻辑分析仪非常重要的部分,典型探头的形状,连接,参数如下图所示。SMI(MDIO)协议分析仪/训练器找欧奥!嘉兴UFS分析仪电话

I2C/SPI协议分析仪/训练器找欧奥!重庆RFFE分析仪收费

终比较结果将对“差分信号高于Vref还是低于Vref?”的问题作出解答:对眼隙的eyescan测量是通过使用不同Vref设置进行一系列eyefinder测量完成的。差分信号的默认eyefinder测量使用Vref=0V。通过将Vref增至零以上。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号。如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。我们会找到信号与上升的Vref值交叉的位置。如果Vref升至足够高,信号的顶部轨迹将通过Vref,我们便会看到眼的顶端。再将Vref升高一点会导致Vcomp保持在Vlo,表示信号不会升至该电之,将Vref移至零以下会看到眼的下半部。eyescan/eyefinder显示窗口会在每个信号的eyescan图下方显示eyefinder交叠部分,以此显示eyefinder与eyescan之间的这一关系。重庆RFFE分析仪收费