商机详情 -

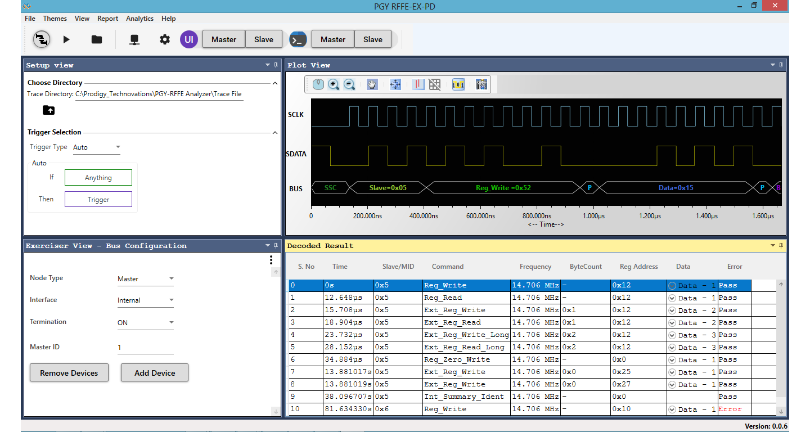

云浮SDIO分析仪收费

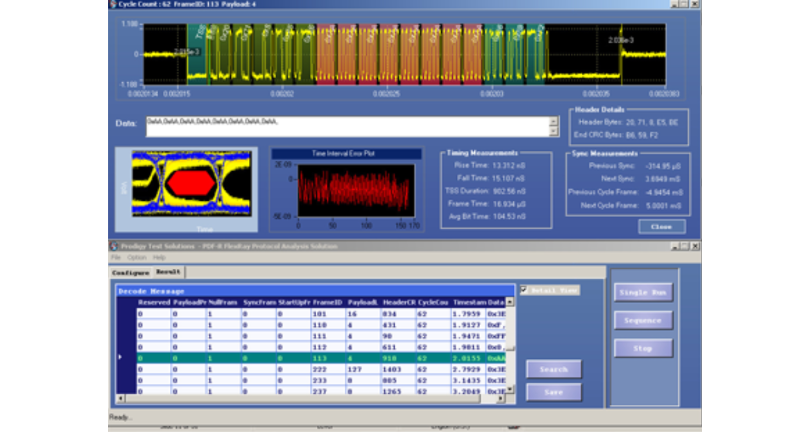

欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。时序和协议是数字系统调试的两大关键点,也是逻辑分析仪能发挥价值的地方。如何使用逻辑分析仪快速地完成接线配置并采集到数据呢?本文以IIC协议为例为大家实测演示。数字系统逻辑关系是通讯研发过程中的关键,它直接影响到整个设备系统能否正常工作。虽然示波器也能做部分数字信号分析,但受限于通道数(一般只有4个通道)和存储深度(较小)。逻辑分析仪可以达到34通道,记录深度长可达2G,再配合数据压缩算法,提高了工程师测试时序分析的效率。下面以IIC为例,分享逻辑分析仪测试步骤。一、准备工作测试主要为被测对象、逻辑分析仪、电脑,IIC协议信号。SMBus协议分析仪/训练器找欧奥!云浮SDIO分析仪收费

这八个触发器都连接到同一时钟信号。图9接收器当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在D0-D7这几条上收集数据。图10总线收集的数据高级触发示例:假设想查看地址值为406F6时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型406F6(十六进制)以及在RD(内存读取)时钟线上查找高电平。图11高级触发设置在配置EdgeAndPatterntrigger(时钟沿和码型触发)对话框时。尝试将该操作看作是构造从左向右读取的句子。Pod、通道和时间标签存储Pod和通道的命名约定:Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。对于模块化的逻辑分析仪。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪。协议分析仪报价UFS协议分析仪/训练器找欧奥!

DampedResistorProbing),电阻匹配探测(ResistiveDividerProbing)。短线探测会增加电容负载。举例:探头电容负载是,连接短线是50欧姆微带线(C=3pF/in),长度1英寸。则整个探头的电容负载是,这个短线是电容负载的主要部分。被测系统可容忍的负载电容是多少呢?需要参考被测电路的系统上升时间,一般规则:短线的电气长度<>PCB传输延迟:150ps/in系统上升时间:500ps则电气长度:则短线长度:(100ps)/(150ps/in)=。如果没法减小短线长度,可以试着用阻尼电阻探测的方式。阻尼电阻有2个作用:隔离来自短线的电容,消减来自短线的反射。图25阻尼电阻探测方式阻尼电阻阻值小的一般规则:目标阻抗的。如果探测环境需要更长的连线,这时候可考虑电阻匹配探测,即在探头尖处附加一个匹配电阻,消除连线的反射。匹配电阻的阻值与连线传输线的阻抗一样即可,但需要考虑信号的衰减。图26电阻匹配探测方式逻辑分析仪的探头主要有3种类型:提前设计型;事后考虑型;定制型。图27逻辑分析仪的探头类型小结:逻辑分析仪探头是逻辑分析仪非常重要的部分,典型探头的形状,连接,参数如下图所示。

没有额外的被测设备)的一小段时间内,可以自动:定位每个通道上的建立/保持窗口。针对尽可能宽的数据有效窗口调整阈电压设置。眼定位是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。眼定位概要:对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置佳采样位置。为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。例如,如果选择盒1上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒1时钟上的上升沿。盒1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。要构建眼定位显示,需要将无数张这样的“照片”堆叠在彼此的顶端。每张“照片”都在T=0时对齐,此时将达到活动时钟沿。照片拍自上升沿还是下降沿并没有关系;它们会在T=0时对齐。构建显示后。PCIE协议分析仪/训练器找欧奥!

如果在时钟沿检测器重置之前出现第二个时钟沿(在个时钟沿后),为避免数据丢失需要两个样本。在跳变定时中,每个序列步骤只有2个分支。在跳变时序中,只有一个全局计数器可用。跳变时序需要有时间标签才能重建数据。通过将时间标签与内存中的测量数据交叉可存储时间标签。默认情况下,分析仪将查找为逻辑分析仪模块定义的所有总线/信号上的转变。但是,为增加可用内存深度和采集时间,可以在高级触发中选择不存储某些总线/信号转变(如将无用信息添加到测量中的时钟或选冲信号)。运行测量时,无论总线/信号是否定义或是否分配给逻辑分析仪通道,都将在所有这些通道上采集数据。在跳变时序模式中,如果定义的总线/信号(未排除的)上存在转变,将保存采集的样本。运行跳变时序测量后,如果为以前未分配的逻辑分析仪通道定义新的总线/信号,那么将显示在这些通道上采集的数据,但是不可能存储这些总线/信号上的所有转变;显示的数据好似新的总线/信号在运行测量前就已经被排除了。在跳变时序中,不需要预先存储数据(触发前获得的样本)。因此,与状态模式非常相似的是,触发位置(起始/中心/结束)表明触发后样本占用内存的百分比。训练器源头工厂,一手劲爆价,就找欧奥!常州I3C分析仪报价

DigRF v4协议分析仪/训练器找欧奥!云浮SDIO分析仪收费

或称为逻辑分析系统),以16900系列逻辑分析系统为例,对应关系如下:插槽从上到下以A至F字母命名。有一条标有Pod2的电缆连接着每一个逻辑分析仪模块。知道某个Pod连接到哪个插槽很重要,因为如果在插槽A和B中都有逻辑分析仪模块,则将有两条盒电缆标有Pod2,但操作界面应用程序会把一条记作SlotAPod2,把另一条记作SlotBPod2。分清这两条电缆很重要。SlotAPod2等于PodA2。A2与SlotAPod2可互相替代;同样,D1与SlotDPod1也可互相替代。时钟Pod(ClockPod)由模块中所有Pod的所有时钟通道组成。每个Pod各有一个时钟通道。所有时钟通道按Clk1、Clk2、Clk3等进行编号。如果某逻辑分析仪模块有两个逻辑分析仪卡,每卡有四个Pod,则该逻辑分析仪的时钟通道标记为Clk1至Clk8。除了Clk1外,时钟通道还可标记为C1。C1和Clk1是一样的。在16900系列逻辑分析系统中,请勿混淆时钟通道C2与SlotC中的Pod2,后者记作PodC2。对于时钟通道,C是Clock的缩写,不是SlotC的缩写。为什么有时Pod会丢失?导致所有Pod对逻辑分析仪模块均不可用的原因有多种:在状态采样模式中,在选择了一般状态模式采样选项的情况下,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下。云浮SDIO分析仪收费