商机详情 -

斗门区时钟晶振推荐厂家

在测试与测量仪器,如示波器、频谱分析仪、信号发生器、网络分析仪中,时钟晶振的性能直接定义了仪器的基本精度指标。这些仪器内部的模数转换器、数模转换器、本地振荡器都需要一个极其纯净和稳定的时钟参考。用于此类仪器的时钟晶振往往是高性能的恒温晶振或温补晶振,它们通过恒温槽或温度补偿网络,将频率温度稳定性提升到±0.1ppm甚至更高的水平。其相位噪声和抖动性能也必须达到仪器级标准,以确保仪器自身的本底噪声足够低,能够精确测量微弱的被测信号。可以说,一台测量仪器的性能上限,在很大程度上由其内部的主参考时钟晶振决定。它是仪器测量准确性和分辨率的物理基石。时钟晶振为FPGA提供全局时钟。斗门区时钟晶振推荐厂家

时钟晶振的相位噪声与时间抖动是衡量其性能的专业指标,对高速通信和精密测量系统尤为关键。相位噪声描述了理想时钟信号在频域上的能量扩散程度,表现为载波两侧的噪声边带;而时间抖动则是这种噪声在时域的直接体现,表现为时钟边沿相对于理想位置的随机偏移。在5G基站、高速SerDes(如PCIe 6.0, 800G以太网)等应用中,参考时钟晶振的相位噪声会直接转化为发射信号的带外杂散和接收机的噪声基底抬升,恶化系统信噪比与链路误码率。评估一颗时钟晶振时,工程师必须详细分析其在关键频偏点(如10Hz, 100Hz, 1kHz, 10kHz, 1MHz)的单边带相位噪声谱密度,以及在不同积分带宽下的随机抖动与确定性抖动。低相位噪声时钟晶振的设计,依赖于高Q值AT切晶体、低噪声振荡电路、精密的温度补偿或恒温控制技术,以及优异的电源噪声抑制能力。光明区3068封装时钟晶振推荐厂家鑫和顺可定制特殊参数的时钟晶振。

时钟晶振的频率精度与全温区稳定性是系统长期可靠工作的基石。初始频率精度指在25°C常温下,输出频率与标称值的偏差,常以±ppm(百万分之一)表示。而评估一颗时钟晶振的稳定性,还需考察其温度稳定性(-40°C至+85°C范围内的总频率变化)、电源电压稳定性(推频系数)、负载稳定性以及长期老化率。例如,工业级应用通常要求时钟晶振在宽温范围内保持±20ppm至±50ppm的稳定性,而通信基站或测量仪器则可能需要±0.5ppm甚至更高的指标。通过采用高稳定性的晶体、精密的模拟或数字温度补偿电路(TCXO)、或恒温槽技术(OCXO),可以大幅提升温度稳定性。低老化率确保了设备在5-10年的生命周期内,时钟基准不会发生漂移,这对于通信、电网、计量等需要长期连续运行的系统至关重要。

可编程时钟晶振(可编程振荡器)表明了时钟源灵活性的发展方向。它内部集成了一个基础时钟晶振、一个锁相环频率合成器和可配置的分频/倍频电路。用户可以通过I2C、SPI等数字接口,配置输出频率、输出格式(LVCMOS/LVDS等)甚至驱动强度,从而在很宽的频率范围内(如1MHz到2.1GHz)输出数十个离散的高精度频率。这种器件用一个硬件型号即可覆盖多种应用需求,极大地简化了物料管理和库存,特别适合产品开发前期频率未确定,或单一硬件平台需要支持多种制式(如多模小基站)的场景。虽然其相位噪声和抖动性能可能略逊于同等级别的固定频率时钟晶振,但其灵活性在许多应用中具有优势。鑫和顺是您可靠的时钟晶振合作伙伴。

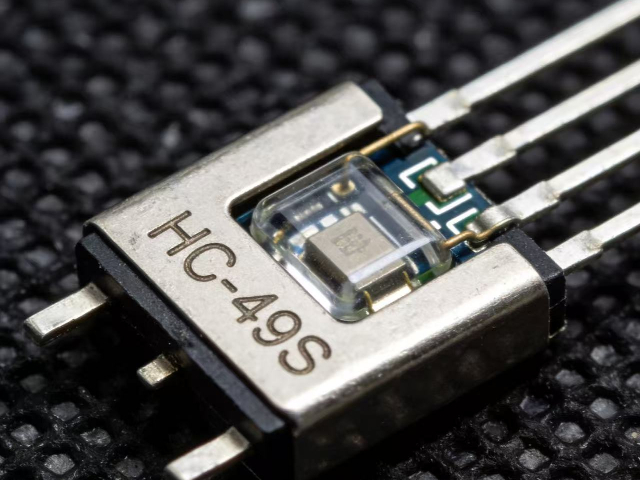

海量物联网终端设备的普及,对时钟晶振提出了微型化、低功耗、高性价比的普适性要求。数以亿计的无线传感器节点、智能标签、可穿戴设备由其内置的微控制器或低功耗无线SoC(如BLE、LoRa、NB-IoT芯片)驱动,这些芯片都需要一个主时钟晶振。物联网用时钟晶振通常工作在16MHz、26MHz、32MHz、40MHz等频率,其挑战是在极低成本和小尺寸(如2016、1612封装)下,实现足够低的功耗(工作电流常低于1mA,睡眠电流极低)和可靠的起振特性。同时,为适应大规模自动化贴装和严峻的成本压力,其设计、生产和测试流程必须高度优化。这类时钟晶振是连接物理世界与数字世界的庞大末梢网络的“基础心跳”,其可靠性与成本直接影响着物联网生态的规模与健康发展。鑫和顺时钟晶振符合RoHS环保标准。福田区308封装时钟晶振批发

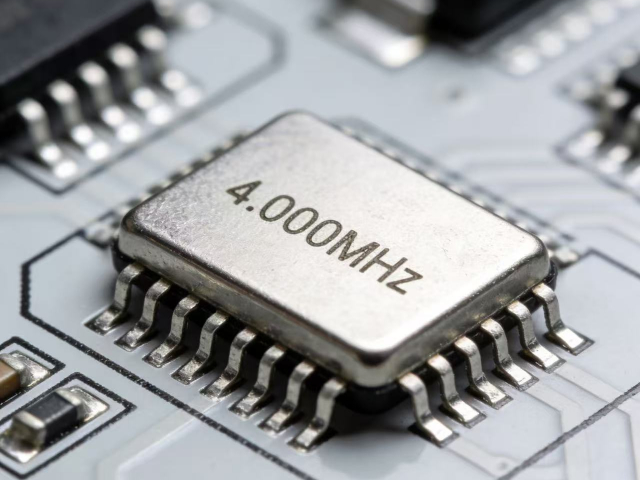

时钟晶振为微处理器提供主时钟信号。斗门区时钟晶振推荐厂家

在多芯片、多板卡构成的复杂电子系统中,时钟信号的分配与完整性保障是重大挑战。时钟晶振作为时钟树的源头,其输出信号的驱动能力、边沿速率和信号质量直接影响下游电路。时钟晶振需要驱动可能存在的传输线损耗、时钟缓冲器的输入电容以及多个分布式负载。为此,其输出需提供符合标准(如LVCMOS、LVDS、LVPECL、HCSL)且边沿受控的波形。过缓的边沿会增加串扰和功耗,过快的边沿则易引起振铃和电磁干扰。工程师需根据负载数量、传输距离及PCB阻抗特性,选择合适的输出类型和驱动强度,并通常在输出端实施恰当的端接策略(如串联阻尼电阻)以抑制反射。良好的布局要求时钟晶振尽量靠近主芯片,并使用完整的参考平面,确保时钟信号从源头到终端都保持干净、陡峭的波形,为系统各模块提供一致的时序参考。斗门区时钟晶振推荐厂家

深圳市鑫和顺科技有限公司汇集了大量的优秀人才,集企业奇思,创经济奇迹,一群有梦想有朝气的团队不断在前进的道路上开创新天地,绘画新蓝图,在广东省等地区的电子元器件中始终保持良好的信誉,信奉着“争取每一个客户不容易,失去每一个用户很简单”的理念,市场是企业的方向,质量是企业的生命,在公司有效方针的领导下,全体上下,团结一致,共同进退,**协力把各方面工作做得更好,努力开创工作的新局面,公司的新高度,未来深圳市鑫和顺科技供应和您一起奔向更美好的未来,即使现在有一点小小的成绩,也不足以骄傲,过去的种种都已成为昨日我们只有总结经验,才能继续上路,让我们一起点燃新的希望,放飞新的梦想!