-

长沙I2C/SPI分析仪售价

发布时间:2026.01.22

长沙I2C/SPI分析仪售价

发布时间:2026.01.22

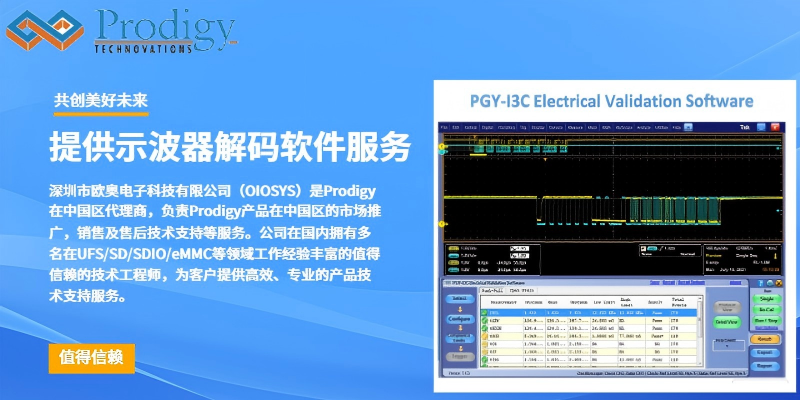

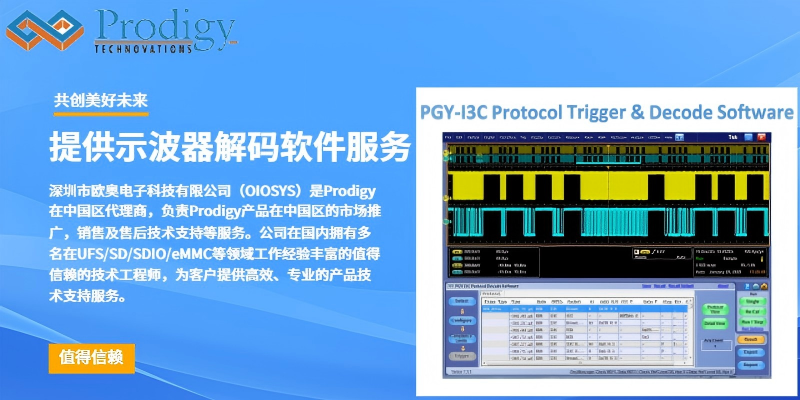

欧奥电子代理Prodigy的I3C测试软件不仅满足MIPI联盟的规范要求,还能与泰克示波器无缝集成,实现电气特性测量与协议分析的双重功能,帮助工程师快速完成合规性验证和故障调试。欧奥电子凭借深厚的...

-

天津逻辑分析仪

发布时间:2026.01.22

天津逻辑分析仪

发布时间:2026.01.22

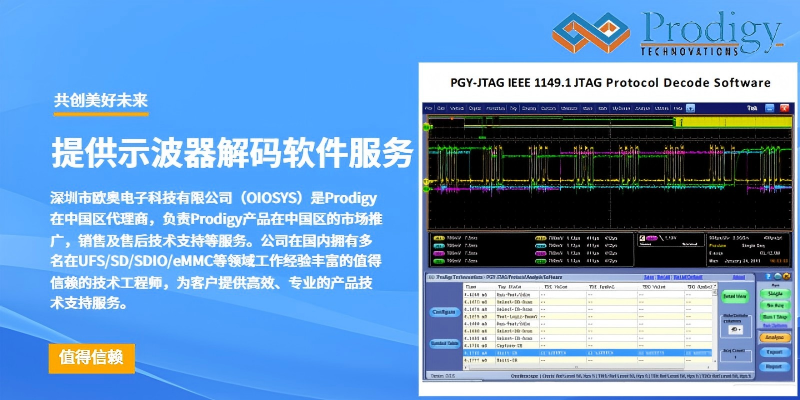

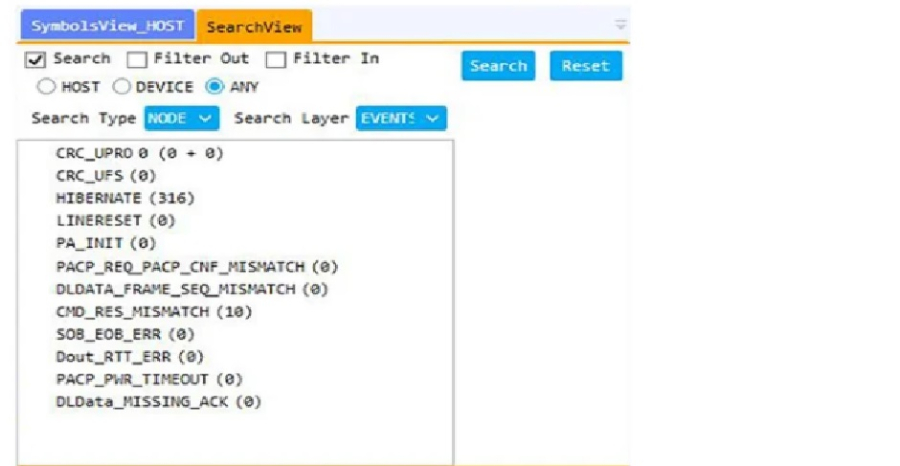

欧奥电子(OIOSYS)是Prodigy在中国区代理商,公司在国内拥有多名在UFS/SD/SDIO/Emmc/PCIe等领域工作经验丰富的值得信赖的技术工程师,为客户提供专业的产品技术支持服务。...

-

湛江HSIC示波器解码软件收费

发布时间:2026.01.21

湛江HSIC示波器解码软件收费

发布时间:2026.01.21

深圳市欧奥电子科技有限公司(OIOSYS)是Prodigy在中国区代理商,负责Prodigy产品在中国区的市场推广,销售及售后技术支持等服务。公司在国内拥有多名在UFS/SD/SDIO/Emmc/PC...

-

赣州I3C示波器解码软件品牌

发布时间:2026.01.21

赣州I3C示波器解码软件品牌

发布时间:2026.01.21

欧奥电子是Prodigy授权的中国区代理商。随着I3C协议向25MbpsDDR模式演进,以及多主设备互联、MCTP协议扩展等新需求出现,示波器解码软件的技术门槛持续提升。Prodigy始终保持技术深耕...

-

连云港USB3.1示波器解码软件

发布时间:2026.01.21

连云港USB3.1示波器解码软件

发布时间:2026.01.21

欧奥电子是Prodigy中国区代理商,欧奥电子的工程师团队可协助客户利用Prodigy软件完成电气参数的极限测试和协议兼容性验证;欧奥电子团队深入了解国内行业需求,I3C协议的广泛应用推动测试解码软件...

-

西安HDMI示波器解码软件找哪家

发布时间:2026.01.20

西安HDMI示波器解码软件找哪家

发布时间:2026.01.20

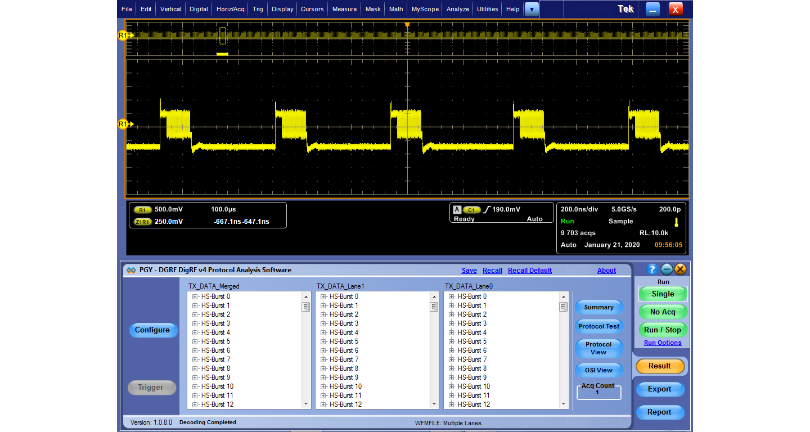

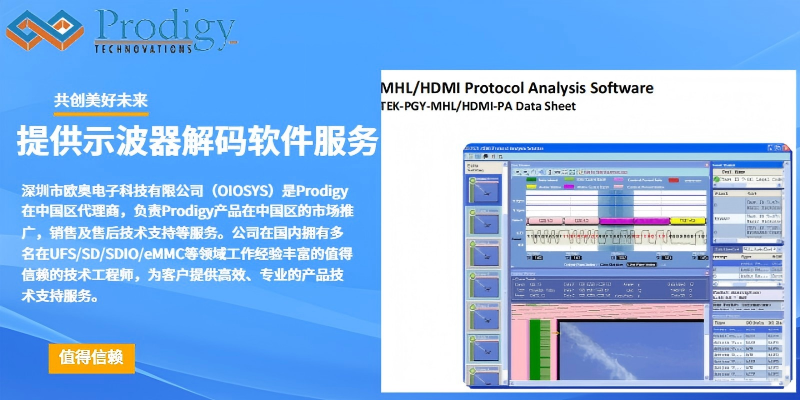

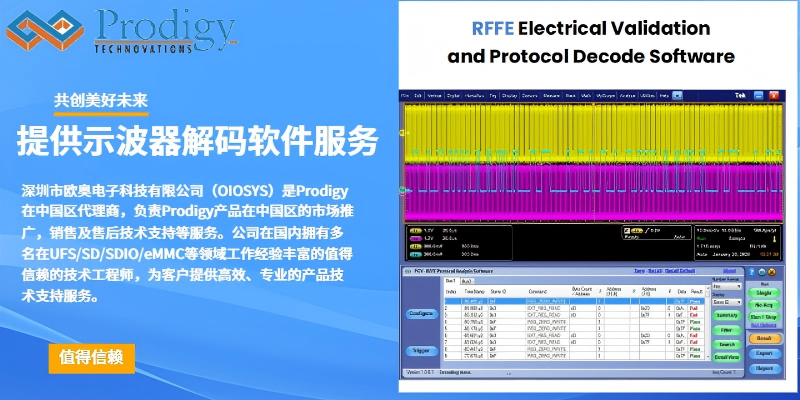

深圳市欧奥电子科技有限公司(OIOSYS)是Prodigy在中国区代理商,负责Prodigy产品在中国区的市场推广,销售及售后技术支持等服务。欧奥电子代理的DigRFv4协议解码软件提供DigRFv4...

-

湛江SPI示波器解码软件电话

发布时间:2026.01.20

湛江SPI示波器解码软件电话

发布时间:2026.01.20

欧奥电子oiosys作为Prodigy品牌在中国区的代理商,凭借专业的技术实力与完善的服务网络,将eMMC、SD、SDIO电气验证和协议解码软件引入国内产业端。eMMC、SD和SDIO电气测量和协...

-

江门HSIC示波器解码软件

发布时间:2026.01.20

江门HSIC示波器解码软件

发布时间:2026.01.20

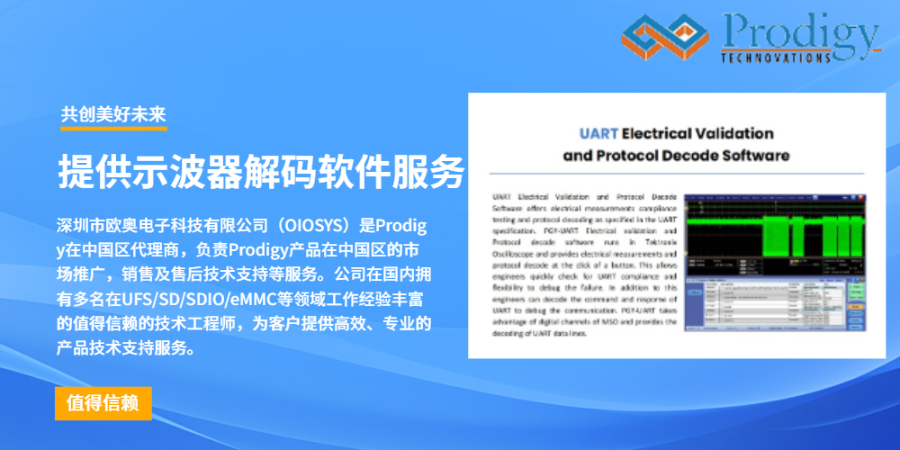

在电子设备研发过程中,UART协议作为常用的串行通信协议之一,其通信稳定性直接影响产品质量,而ProdigyUART示波器解码软件性能表现良好,成为众多企业的选择的测试工具。该软件不仅支持传统UART...

-

南宁SPMI示波器解码软件报价

发布时间:2026.01.19

南宁SPMI示波器解码软件报价

发布时间:2026.01.19

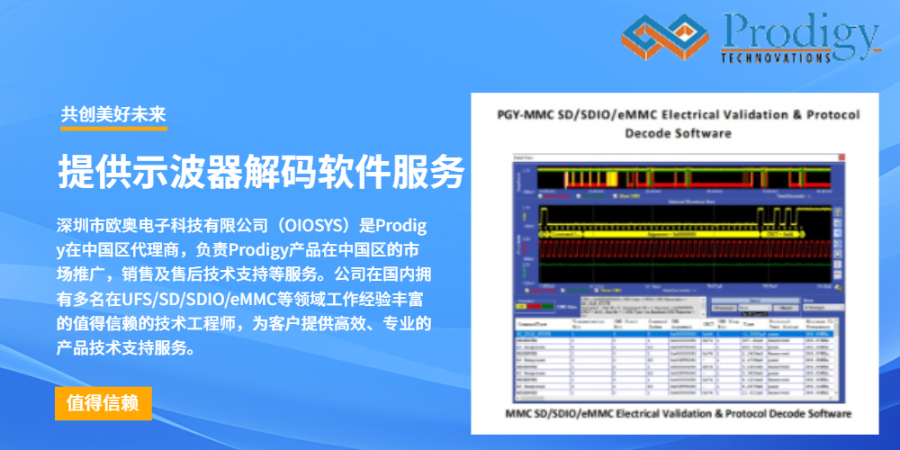

深圳市欧奥电子科技有限公司(OIOSYS)是Prodigy在中国区代理商,欧奥电子(OIOSYS)代理的eMMC、SD和SDIO电气测量和协议解码软件可在泰克示波器上运行,符合eMMC4.51和5.0...

-

温州I2C示波器解码软件报价

发布时间:2026.01.19

温州I2C示波器解码软件报价

发布时间:2026.01.19

欧奥电子专注提供芯片研发测试用的各类协议分析仪,示波器解码软件及电性测试软件,是Prodigy中国区代理商,专注提供Prodigy示波器解码软件,例如I2C、I2S、I3C、SPI、QSPI、eSPI...

-

济南SPMI示波器解码软件费用

发布时间:2026.01.19

济南SPMI示波器解码软件费用

发布时间:2026.01.19

深圳市欧奥电子科技有限公司致力于为芯片测试解决方案提供各类协议分析仪,示波器解码软件和电性测试软件。SMBus示波器解码软件提供SMBus规范(版)规定的电气测量和测试以及协议解码。PGY-SMBus...

-

嘉兴DigRF v4示波器解码软件哪家好

发布时间:2026.01.19

嘉兴DigRF v4示波器解码软件哪家好

发布时间:2026.01.19

在电子设备研发过程中,UART协议作为常用的串行通信协议之一,其通信稳定性直接影响产品质量,而ProdigyUART示波器解码软件性能表现良好,成为众多企业的选择的测试工具。该软件不仅支持传统UART...

-

天津协议分析仪价格

发布时间:2026.01.18

天津协议分析仪价格

发布时间:2026.01.18

欧奥电子oiosys专注提供ProdigyI2C与SPI协议分析仪。I2CSPI协议的复杂性要求分析仪具备强大的硬件性能与灵活的软件适配能力,Prodigy在这两方面均展现出行业水平。硬件层面,其采...

-

哈尔滨RFFE示波器解码软件哪家好

发布时间:2026.01.18

哈尔滨RFFE示波器解码软件哪家好

发布时间:2026.01.18

欧奥电子是Prodigy中国区代理商,专注为芯片研发测试提供测试解决方案用的各类协议分析仪,示波器解码软件和电性测试软件。在消费电子、工业控制等领域,eMMC、SD及SDIO接口已成为存储与数据传输...

-

湛江USB3.0示波器解码软件收费

发布时间:2026.01.18

湛江USB3.0示波器解码软件收费

发布时间:2026.01.18

欧奥电子(OIOSYS)是Prodigy在中国区代理商,公司在国内拥有多名在UFS/SD/SDIO/Emmc/PCIe等领域工作经验丰富的值得信赖的技术工程师,为客户提供专业的产品技术支持服务。欧奥电...

-

中山FlexRay示波器解码软件服务商

发布时间:2026.01.18

中山FlexRay示波器解码软件服务商

发布时间:2026.01.18

随着数字通信技术飞速发展,SPI(串行外设接口)协议因高速、全双工、同步通信的特性,已广泛应用于消费电子、汽车电子、工业控制、航空航天等众多领域。而SPI协议解码软件作为芯片研发与设备测试环节的关键...

-

石家庄I2C示波器解码软件服务商

发布时间:2026.01.18

石家庄I2C示波器解码软件服务商

发布时间:2026.01.18

欧奥电子是Prodigy中国区代理商,专注为芯片研发测试提供测试解决方案用的各类协议分析仪,示波器解码软件和电性测试软件。在消费电子、工业控制等领域,eMMC、SD及SDIO接口已成为存储与数据传输...

-

西安I2S示波器解码软件品牌

发布时间:2026.01.18

西安I2S示波器解码软件品牌

发布时间:2026.01.18

作为Prodigy在中国区的官方代理商,欧奥电子oiosys将Prodigy协议分析产品引入国内,为消费电子、汽车、航空航天等领域提供了从UFS到车载以太网的全场景测试解决方案。欧奥电子供应的Prod...

-

江门QSPI示波器解码软件

发布时间:2026.01.18

江门QSPI示波器解码软件

发布时间:2026.01.18

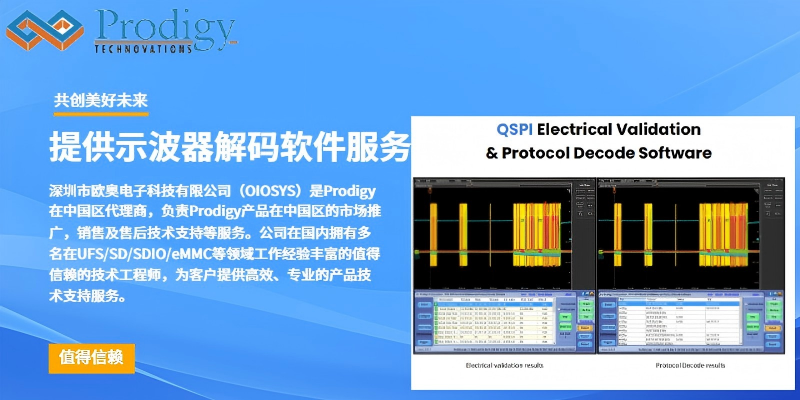

作为Prodigy在中国区的官方代理商,欧奥电子oiosys将Prodigy协议分析产品引入国内,为消费电子、汽车、航空航天等领域提供了从UFS到车载以太网的全场景测试解决方案。欧奥电子供应的Prod...

-

太原RFFE示波器解码软件品牌

发布时间:2026.01.18

太原RFFE示波器解码软件品牌

发布时间:2026.01.18

欧奥电子oiosys提供Prodigy协议分析仪、SI测试软件以及示波器协议解码软件,例如I2C、I2S、I3C、SPI、QSPI、eSPI、UART、SMBus、RFFE、SPMI、eMMC、SD、...

-

合肥10Base T1S示波器解码软件费用

发布时间:2026.01.18

合肥10Base T1S示波器解码软件费用

发布时间:2026.01.18

深圳市欧奥电子科技有限公司(OIOSYS)是Prodigy在中国区代理商,负责Prodigy产品在中国区的市场推广,销售及售后技术支持等服务。公司在国内拥有多名在UFS/SD/SDIO/Emmc/PC...

-

海南HDMI示波器解码软件服务商

发布时间:2026.01.18

海南HDMI示波器解码软件服务商

发布时间:2026.01.18

欧奥电子OIOSYS是Prodigy在中国区代理商,负责Prodigy产品在中国区的市场推广,销售及售后技术支持等服务。欧奥电子专业提供I2C电气验证和协议解码软件,该软件提供I2C规范规定的电气测量...

-

杭州USB3.0示波器解码软件售价

发布时间:2026.01.18

杭州USB3.0示波器解码软件售价

发布时间:2026.01.18

欧奥电子是Prodigy中国区代理商,产品有嵌入式设备的UFS、PCIE、SRIO、I3C、I2CSPI、SPMI等协议分析仪及示波器解码软件和电性测试软件。Prodigy的FlexRay协议解码和S...

-

惠州UART逻辑分析仪品牌

发布时间:2026.01.17

惠州UART逻辑分析仪品牌

发布时间:2026.01.17

小编将对AOC27G2电竞显示器的色温一致性予以测评,一起来了解下吧。具体测评数据如下所示:在色温一致性方面,AOC27G2电竞显示器的白点色温稳定在7300K,色温整体稍微有些偏冷。以上便是小编此次...

-

梅州USB3.0示波器解码软件售价

发布时间:2026.01.17

梅州USB3.0示波器解码软件售价

发布时间:2026.01.17

欧奥电子专注提供Prodigy高速低速协议训练器和分析解决方案,产品包括示波器解码软件和电性测试软件。欧奥电子代理Prodigy的示波器解码软件型号有I2C、I2S、SPI、I3C、eMMCSDSDI...

-

连云港eMMC(4.41

发布时间:2026.01.17

连云港eMMC(4.41

发布时间:2026.01.17

欧奥电子oiosys作为Prodigy品牌在中国区的代理商,凭借专业的技术实力与完善的服务网络,将eMMC、SD、SDIO电气验证和协议解码软件引入国内产业端。eMMC、SD和SDIO电气测量和协...

-

成都10Base T1S示波器解码软件

发布时间:2026.01.17

成都10Base T1S示波器解码软件

发布时间:2026.01.17

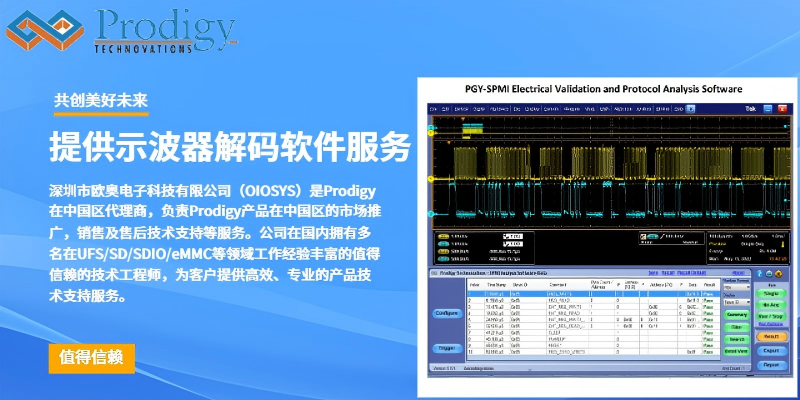

欧奥电子专业提供Prodigy各类协议分析仪,示波器解码软件和电性测试软件。PGY-SPMI电气验证和协议解码软件可在泰克示波器中运行,只需点击按钮即可进行电气测量和协议解码。该软件可灵活设置电气测量...

-

郑州SPMI示波器解码软件售价

发布时间:2026.01.17

郑州SPMI示波器解码软件售价

发布时间:2026.01.17

欧奥电子代理的Prodigy协议分析仪、示波器解码软件以及电性测试软件。PGY-SPI示波器解码软件可利用MSO的数字通道,对SPI数据线进行解码。利用可定制的SPI电信号参考电平自动进行电气测量,自...

-

南京SSIC示波器解码软件厂家

发布时间:2026.01.17

南京SSIC示波器解码软件厂家

发布时间:2026.01.17

欧奥电子专业提供Prodigy各类协议分析仪,示波器解码软件和电性测试软件。PGY-SPMI电气验证和协议解码软件可在泰克示波器中运行,只需点击按钮即可进行电气测量和协议解码。该软件可灵活设置电气测量...

-

阳江eMMC SD SDIO示波器解码软件服务商

发布时间:2026.01.17

阳江eMMC SD SDIO示波器解码软件服务商

发布时间:2026.01.17

作为Prodigy在中国区的官方代理商,欧奥电子oiosys将Prodigy协议分析产品引入国内,为消费电子、汽车、航空航天等领域提供了从UFS到车载以太网的全场景测试解决方案。欧奥电子供应的Prod...