商机详情 -

广州HJT异质结PECVD

异质结是指两种不同材料(通常是半导体材料)之间的接触界面。由于材料的物理性质(如能带结构、电导率、介电常数等)不同,这种界面会形成特殊的电学和光学特性。异质结(Heterojunction)是由两种不同禁带宽度的半导体材料(如不同元素构成的半导体,或同种元素但晶体结构、掺杂类型不同的半导体),通过特定工艺紧密接触形成的界面结构。其关键特点是两种材料的能带结构不连续,从而在界面处产生独特的物理效应。关键要素材料差异:两种半导体的禁带宽度(Eg)不同,常见组合如硅(Si)与氮化镓(GaN)、砷化镓(GaAs)与磷化铟(InP)等。界面特性:由于材料差异,界面处会形成能带弯曲和内建电场,明显改变载流子(电子、空穴)的运动行为。与同质结的区别同质结:由同种半导体材料(如纯硅)形成的结(如 p-n 结),能带连续,载流子限制能力较弱。异质结:能带不连续,可通过设计材料组合精细调控载流子的分布与输运,性能更优(如更高效率、更快速度)。异质结电致变色玻璃,调光响应速度0.5秒完成。广州HJT异质结PECVD

异质结(Heterojunction)是指由两种不同材料组成的半导体结。由于材料不同,它们的能带结构在界面处会发生变化,形成独特的电学和光学性质。异质结广泛应用于光电子器件、太阳能电池和半导体器件中。异质结是由两种不同半导体材料(通常是不同禁带宽度的材料)组成的界面。这种界面可以是 abrupt(突变)或 graded(渐变)的。由于材料不同,界面处的能带结构会发生变化,通常表现为能带的弯曲或偏移。根据能带对齐方式,异质结可以分为以下几种类型:突变异质结(Abrupt Heterojunction):两种材料的能带结构在界面处突然变化。渐变异质结(Graded Heterojunction):两种材料的能带结构在界面处逐渐变化。齐带异质结(Lattice-Matched Heterojunction):两种材料的晶格常数匹配,界面处无晶格失配应力。非齐带异质结(Non-Lattice-Matched Heterojunction):两种材料的晶格常数不匹配,界面处存在晶格失配应力。广州HJT异质结PECVD釜川(无锡)智能科技,异质结开创能源新纪元。

异质结太阳能电池使用晶体硅片进行载流子传输和吸收,并使用非晶/或微晶薄硅层进行钝化和结的形成。顶部电极由透明导电氧化物(TCO)层和金属网格组成。异质结硅太阳能电池已经吸引了很多人的注意,因为它们可以达到很高的转换效率,可达26.3%,相关团队对HJT极限效率进行更新为28.5%,同时使用低温度加工,通常整个过程低于200℃。低加工温度允许处理厚度小于100微米的硅晶圆,同时保持高产量。异质结电池具备光电转化效率提升潜力高、更大的降成本空间、更高的双面率、可有效降低热损失、更低的光致衰减、制备工艺简单等特点,为光伏领域带来了新的希望。

异质结具有许多优势。首先,由于不同材料的能带结构不同,异质结可以实现更高的电子迁移率和更低的电阻。其次,通过选择不同的材料组合,可以调节异质结的能带偏移,从而实现特定的电子器件功能。然而,异质结的制备和性能控制也面临一些挑战。例如,材料的生长和界面的质量对异质结的性能至关重要,而这些方面的控制往往较为复杂。此外,不同材料之间的晶格不匹配也可能导致晶体缺陷和界面应力,影响异质结的性能。在设计异质结时,材料的选择至关重要。通常选择的材料具有互补的能带结构和晶格匹配性,以实现良好的界面质量和电子传输性能。例如,在二极管中,常用的材料组合是硅和锗,它们具有相似的晶格常数和能带结构。此外,通过在异质结中引入掺杂原子,还可以调节材料的电子性质,进一步优化器件性能。釜川异质结,品质铸就能源传奇。

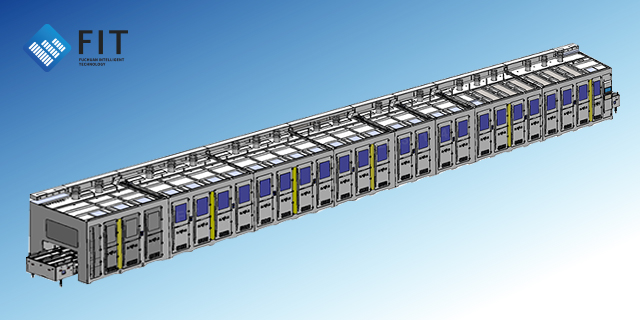

光伏高效异质结电池整线解决方案,产业机遇:方向清晰:HJT技术工艺流程短、功率衰减低、输出功率稳定、双面发电增益高、未来主流技术方向;时间明确:HJT平均量产效率已超过PERC瓶颈(25%),行业对HJT电池投入持续加大,电池商业化已逐渐成熟;机遇可期:设备与耗材是HJT规模化的关键,降本增效是不变的主题,具备HJT整线整合能力的供应商优势明显。当前HJT生产成本约:硅片占比约50%,银浆占比约25%,靶材约6%左右;当前HJT设备成本约:清洗制绒设备、PECVD设备、PVD设备、丝网印刷,设备投资额占比分别约10%、50%、25%和15%。手术机器人配置异质结力传感器,操作反馈延迟低于1ms。广州HJT异质结PECVD

釜川(无锡)智能科技,异质结技术驱动者,让智能科技更高效、更可靠!广州HJT异质结PECVD

太阳能异质结电池工艺1.清洗制绒。通过腐蚀去除表面损伤层,并且在表面进行制绒,以形成绒面结构达到陷光效果,减少反射损失;2.正面/背面非晶硅薄膜沉积。通过CVD方式在正面/背面分别沉积5~10nm的本征a-Si:H,作为钝化层,然后再沉积掺杂层;3.正面/背面TCO沉积。通过PVD在钝化层上面进行TCO薄膜沉积;4.栅线电极。通过丝网印刷进行栅线电极制作;5.烘烤(退火)。通过丝网印刷进行正面栅线电极制作,然后通过低温烧结形成良好的接触;6.光注入。7.电池测试及分选。广州HJT异质结PECVD