商机详情 -

安徽芯片ATS2835P2

功放芯片与音频 codec(编解码器)是音频系统中相辅相成的两个主要组件,二者的协同工作直接决定音频信号的处理质量。音频 codec 的主要功能是将数字音频信号(如手机存储的 MP3 文件)转化为模拟音频信号,或反之将模拟信号数字化,同时具备音量调节、降噪、音效处理等功能;而功放芯片则负责将 codec 输出的微弱模拟信号放大,驱动扬声器发声。在工作过程中,二者需保持信号格式与参数的匹配,比如 codec 输出的信号幅度需符合功放芯片的输入范围(通常为几百毫伏),若信号过强可能导致功放芯片过载失真,过弱则会增加噪声比例。为实现高效协同,部分厂商会推出集成 codec 与功放功能的单芯片解决方案,减少外部电路连接,降低信号传输损耗与干扰,同时简化系统设计,如某型号芯片集成了 24 位音频 codec 与 D 类功放,支持采样率高达 192kHz,既能保证音频信号的高保真转换,又能实现高效功率放大,广泛应用于智能音箱、平板电脑等设备。此外,二者还需通过 I2C、SPI 等通信接口实现参数配置协同,如 codec 调节输出信号增益时,功放芯片需同步调整输入增益,确保整体音效稳定。12S数字功放芯片内置温度传感器与风扇控制接口,当芯片温度超过85℃时自动启动散热流程。安徽芯片ATS2835P2

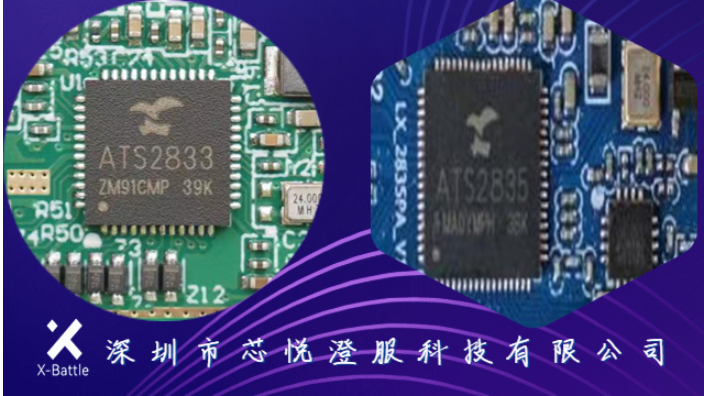

蓝牙音响芯片作为蓝牙音响的重要组件,犹如人的心脏一般,掌控着整个音响系统的运行。它负责实现蓝牙信号的高效接收与准确处理,将来自手机、电脑等设备的音频信号,顺畅地转换为音响能够识别并播放的格式。以常见的炬芯 ATS 系列芯片为例,其内部集成了复杂的电路结构,涵盖蓝牙通信模块、音频解码模块以及功率放大控制模块等。在实际工作中,当手机通过蓝牙发送音频数据时,芯片的蓝牙通信模块率先捕捉信号,迅速传递至音频解码模块,准确解析数据后,再由功率放大控制模块调节信号强度,驱动扬声器发声,为用户带来美妙的听觉享受,其地位无可替代。江苏芯片ATS2835P蓝牙音响芯片能与其他设备快速配对,即连即享音乐播放。

蓝牙音响芯片对于蓝牙音响音质起着决定性的作用。从音频信号的接收、解码到功率放大输出,每一个环节都依赖芯片的准确处理。首先,芯片的蓝牙接收模块要能够稳定、快速地接收来自音源设备的音频信号,避免信号丢失或干扰,为高质量音频传输奠定基础。在音频解码阶段,芯片所支持的解码格式与解码算法直接影响音频的还原度。例如,支持高解析音频解码的芯片能够还原出更多音乐细节,使声音更加真实、生动。功率放大模块则决定了扬声器能够获得的驱动功率,合适的功率输出能够让扬声器充分发挥性能,展现出饱满、有力的声音。不同品牌、型号的蓝牙音响芯片在音质表现上存在明显差异,质优芯片能够打造出优良的音质,为用户带来身临其境的音乐享受,而低质量芯片则可能导致音质失真、单薄,无法满足用户对品质高的音乐的追求。

ATS2853P2芯片采用成熟工艺制程(如40nm),且厂商承诺提供至少10年供货周期,避免因停产导致的供应链风险。在2024-2025年全球芯片短缺期间,实测交货周期稳定在8周以内。设计时需与厂商签订长期供货协议,并预留一定库存以应对突发需求。厂商与主流音频算法公司(如Waves、Dolby)建立合作,提供预置音效库及调音工具,开发者可直接调用专业音效参数,无需从头开发。在家庭影院场景中,实测使用预置音效后,声场宽度提升40%,定位精度提高25%。设计时需在固件中预留算法接口,以支持后续生态扩展。智能会议音响设备采用ACM8623,其低底噪与数字信号处理能力,确保会议发言清晰无杂音,提升沟通效率。

蓝牙音响芯片技术的飞速发展深刻地影响着蓝牙音响的设计理念与产品形态。一方面,随着芯片集成度的不断提高、功耗的降低以及性能的增强,蓝牙音响的设计更加趋于小型化、轻薄化。例如,由于芯片体积的减小,设计师可以将更多的空间用于优化音响的外观造型与内部结构,打造出更加精致、时尚的产品。另一方面,芯片所具备的强大功能,如智能语音交互、品质高的音频解码、多种音效增强技术等,促使蓝牙音响的功能更加丰富多样。设计师可以根据芯片的功能特点,开发出具有独特卖点的产品,如具备智能语音助手功能的蓝牙音响,满足用户对智能生活的追求;支持高解析音频解码的蓝牙音响,为音乐发烧友提供更质优的音频体验。芯片技术的进步为蓝牙音响的设计创新提供了广阔的空间,推动着蓝牙音响产品不断向更高水平发展。12S数字功放芯片支持Dolby Atmos虚拟化,通过HRTF头部相关传输函数模拟7.1.4声道空间音频。江苏芯片ATS2835P

支持多麦克风 ENC 的蓝牙音响芯片,优化通话与语音交互质量。安徽芯片ATS2835P2

ATS2853P2提供I2S TX/RX、SPDIF TX/RX、UART、SPI、I2C及7个GPIO接口,支持连接外部Codec、功放及传感器。其中I2S接口支持主从模式切换,比较高采样率192kHz,可直连Hi-Res音频解码芯片。设计时需在I2S数据线上串联22Ω电阻,以匹配阻抗并减少信号反射,实测可降低时钟抖动至50ps以内。内置16MB SPI Nor Flash用于存储固件,支持通过SPP/BLE透传协议进行OTA升级,单次升级包大小可达4MB。设计时需在Flash芯片VCC引脚并联10μF钽电容,以抑制电源波动导致的编程错误,实测可降低固件烧录失败率至0.1%以下。安徽芯片ATS2835P2