在移动设备、服务器、游戏系统和网络存储等现代应用中,对增加存储容量的需求不断增长。为了满足这一需求,其中许多设备正在过渡到使用 PCIe 上的 NVMe 协议的固态硬盘 (SSD)。虽然 PCIe 传统上被认为是一种高耗电的接口,但 PCI-SIG(PCI 特别兴趣小组)一直在不断发展 PCIe 规范,以提高性能,同时降低功耗,特别是支持新兴的功耗敏感型应用。

对于电池供电的设备,在不完全关闭设备的情况下实现快速唤醒时间和更长的电池寿命至关重要。此外,当 PCIe 接口空闲时,它必须消耗少的功率,并且能够无缝地返回到活动状态,而不会降低用户体验。

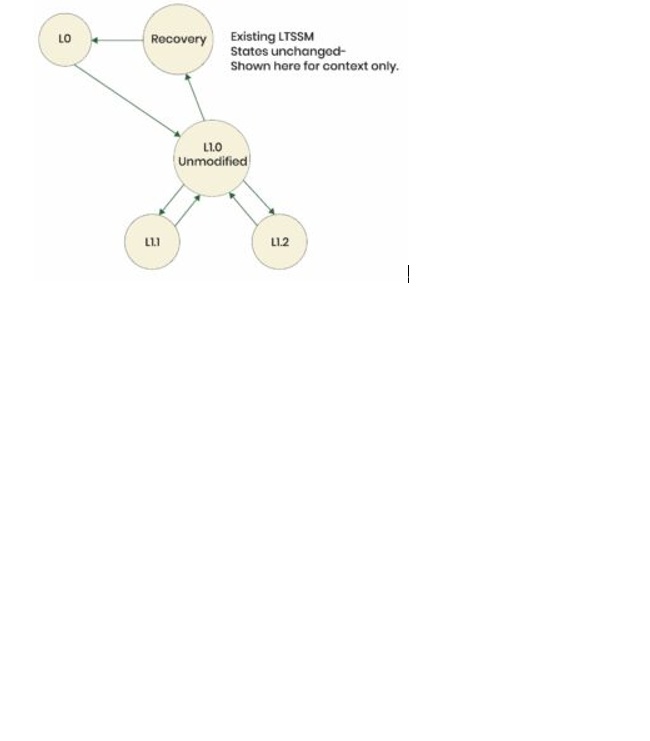

为了满足这些要求,PCI-SIG 引入了 L1 子状态(L1.1 和 L1.2)作为 PCIe 电源管理架构的一部分。这些子状态利用现有的 CLKREQ# 信号,该信号经过扩展以支持用于功率控制的额外信号。这允许 PCIe 收发器在不活动期间关闭其高速电路,并在需要时使用 CLKREQ# 唤醒它们。

借助 L1 子状态,功耗可以降低——从活动 L0 状态下的大约 400-500 mW 降低到 L1.2 状态下的2-3 mW,从而在保持响应能力的同时实现节能。

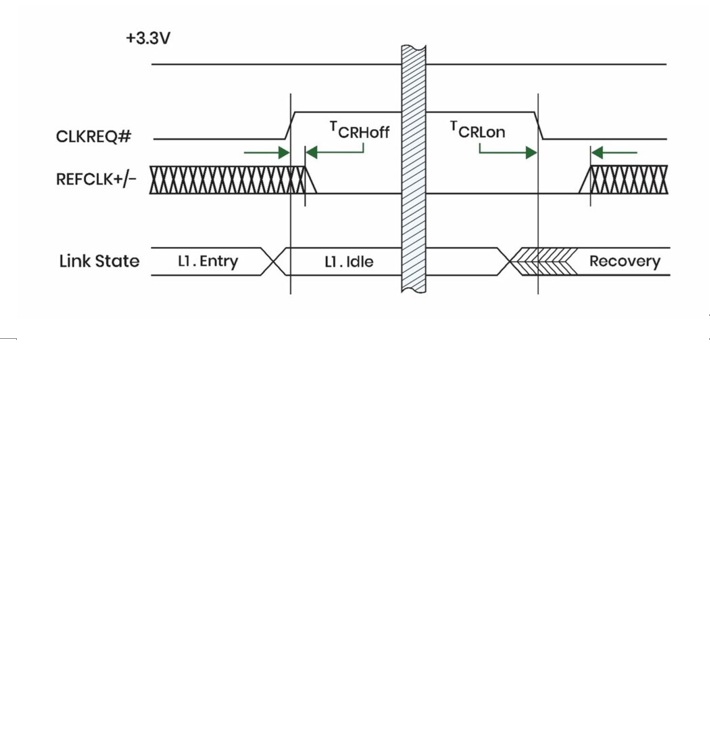

为了确保不同根 complex 和 end 点之间的互作性,需要保持到 CLKREQ 和 REFCLK 之间的 timing 。PCI-SIG 建议的时序值为

上电 CLKREQ# 时序

|

象征 |

参数 |

min |

max |

单位 |

注意 |

|

TCRHoff |

CLKREQ# 取消置低高电平到时钟停放 |

0 |

|

夜行者 |

|

|

TCRLon |

CLKREQ# 断言低电平至时钟有效 |

|

400 |

夜行者 |

请参阅注释 |

注意:当设备支持并启用 LTR 时,允许 T CRLon 超过此值。延迟容差报告 (LTR) 机制允许设备通知主机 (Root Complex) 在必须处理其请求(例如中断或内存访问)之前,它可以容忍延迟多长时间。这有助于主机协调电源管理并有效地安排跨多个设备的服务,而不会影响性能。LTR 信息在 PCIe 链路启动阶段交换,作为配置和训练序列的一部分,使主机能够在满足设备延迟要求的同时,在进入低功耗状态时做出明智的决策。

想要了解更多信息?加入我们的网络研讨会,主题为“开机和低功耗状态下的PCIe边带信号功能概述以及验证“。

Prodigy Technovations 提供 PCIe 低功耗边带信号分析仪,帮助您捕获和分析电源转换期间的关键信号行为。